RM0008 Flexible static memory controller (FSMC)

Doc ID 13902 Rev 12 521/1096

21.5.6 NOR/PSRAM controller registers

The peripheral registers have to be accessed by words (32-bit).

SRAM/NOR-Flash chip-select control registers 1..4 (FSMC_BCR1..4)

Address offset: 0xA000 0000 + 8 * (x – 1), x = 1...4

Reset value: 0x0000 30DX

This register contains the control information of each memory bank, used for SRAMs, ROMs

and asynchronous or burst NOR Flash memories.

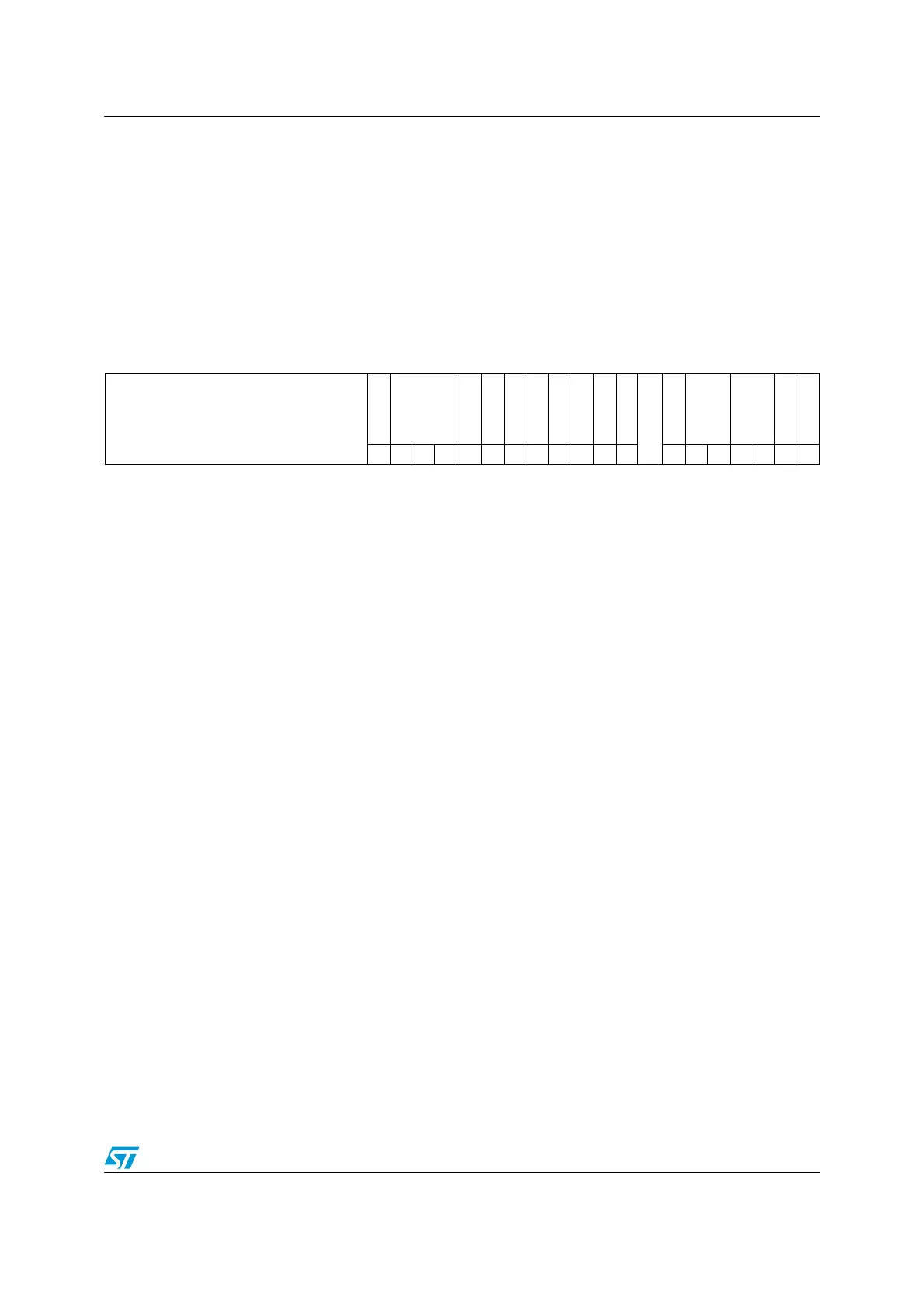

313029282726252423222120191817161514131211109876543210

Reserved

CBURSTRW

Reserved

ASCYCWAIT

EXTMOD

WAITEN

WREN

WAITCFG

WRAPMOD

WAITPOL

BURSTEN

Reserved

FACCEN

MWID

MTYP

MUXEN

MBKEN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 19 CBURSTRW: Write burst enable.

For Cellular RAM, the bit enables synchronous burst protocol during write operations. For Flash

memory access in burst mode, this bit enables/disables the wait state insertion via the NWAIT

signal. The enable bit for the synchronous burst protocol during read access is the BURSTEN bit in

the FSMC_BCRx register.

0: Write operations are always performed in asynchronous mode

1: Write operations are performed in synchronous mode.

Bit 15 ASYNCWAIT: Wait signal during asynchronous transfers

This bit enables the FSMC to use the wait signal even during an asynchronous protocol.

0: NWAIT signal is not taken in to account when running an asynchronous protocol (default after

reset)

1: NWAIT signal is taken in to account when running an asynchronous protocol

Bit 14 EXTMOD: Extended mode enable.

This bit enables the FSMC to program inside the FSMC_BWTR register, so it allows different

timings for read and write.

0: values inside FSMC_BWTR register are not taken into account (default after reset)

1: values inside FSMC_BWTR register are taken into account

Bit 13 WAITEN: Wait enable bit.

For Flash memory access in burst mode, this bit enables/disables wait-state insertion via the

NWAIT signal:

0: NWAIT signal is disabled (its level not taken into account, no wait state inserted after the

programmed Flash latency period)

1: NWAIT signal is enabled (its level is taken into account after the programmed Flash latency

period to insert wait states if asserted) (default after reset)

Bit 12 WREN: Write enable bit.

This bit indicates whether write operations are enabled/disabled in the bank by the FSMC:

0: Write operations are disabled in the bank by the FSMC, an AHB error is reported,

1: Write operations are enabled for the bank by the FSMC (default after reset).

Loading...

Loading...