Serial peripheral interface (SPI) RM0008

720/1096 Doc ID 13902 Rev 12

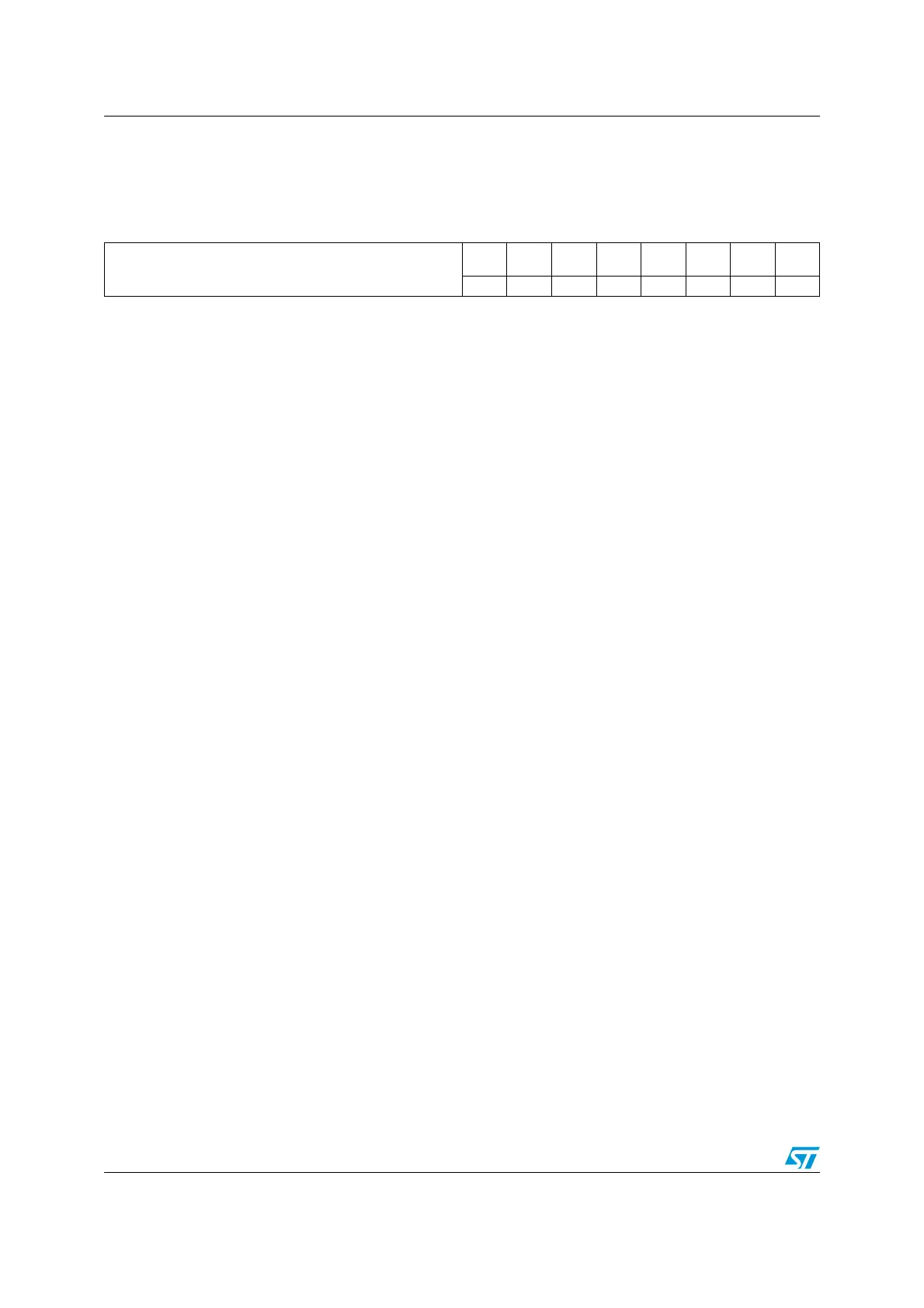

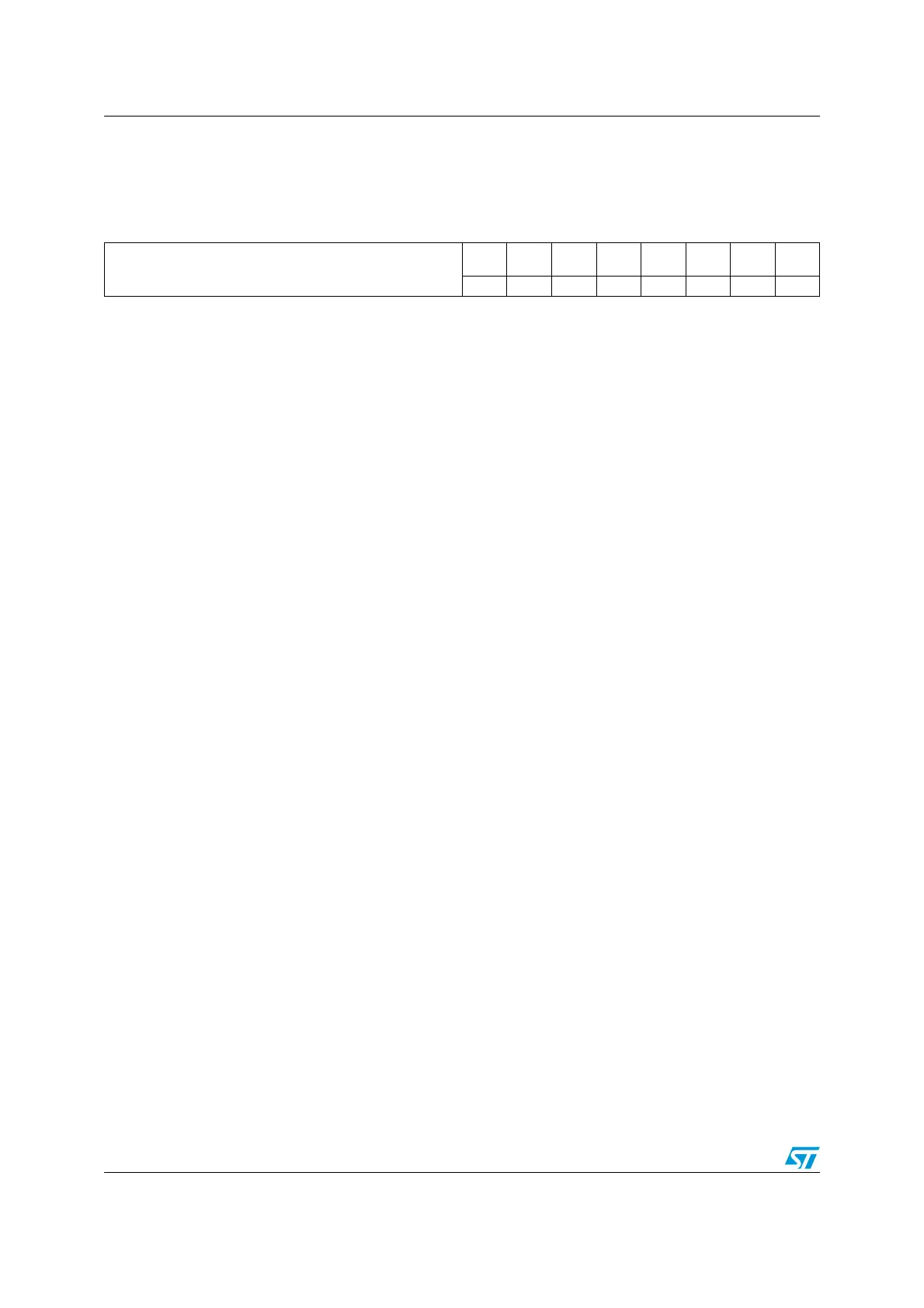

25.5.3 SPI status register (SPI_SR)

Address offset: 0x08

Reset value: 0x0002

1514131211109876543210

Reserved

BSY OVR MODF

CRC

ERR

UDR

CHSID

E

TXE RXNE

rrrrc_w0rrrr

Bits 15:8 Reserved. Forced to 0 by hardware.

Bit 7 BSY: Busy flag

0: SPI (or I2S)not busy

1: SPI (or I2S)is busy in communication or Tx buffer is not empty

This flag is set and cleared by hardware.

Note: BSY flag must be used with caution: refer to Section 25.3.7: Status flags and

Section 25.3.8: Disabling the SPI.

Bit 6 OVR: Overrun flag

0: No overrun occurred

1: Overrun occurred

This flag is set by hardware and reset by a software sequence. Refer to Section 25.4.7 on

page 714 for the software sequence.

Bit 5 MODF: Mode fault

0: No mode fault occurred

1: Mode fault occurred

This flag is set by hardware and reset by a software sequence. Refer to Section 25.3.10 on

page 695 for the software sequence.

Note: Not used in I

2

S mode

Bit 4 CRCERR: CRC error flag

0: CRC value received matches the SPI_RXCRCR value

1: CRC value received does not match the SPI_RXCRCR value

This flag is set by hardware and cleared by software writing 0.

Note: Not used in I

2

S mode

Bit 3 UDR: Underrun flag

0: No underrun occurred

1: Underrun occurred

This flag is set by hardware and reset by a software sequence. Refer to Section 25.4.7 on

page 714 for the software sequence.

Note: Not used in SPI mode

Bit 2 CHSIDE: Channel side

0: Channel Left has to be transmitted or has been received

1: Channel Right has to be transmitted or has been received

Note: Not used for the SPI mode. No meaning in PCM mode

Bit 1 TXE: Transmit buffer empty

0: Tx buffer not empty

1: Tx buffer empty

Bit 0 RXNE: Receive buffer not empty

0: Rx buffer empty

1: Rx buffer not empty

Loading...

Loading...