RM0008 Interrupts and events

Doc ID 13902 Rev 12 201/1096

10.3 EXTI registers

Refer to Section 2.1 on page 46 for a list of abbreviations used in register descriptions.

The peripheral registers have to be accessed by words (32-bit).

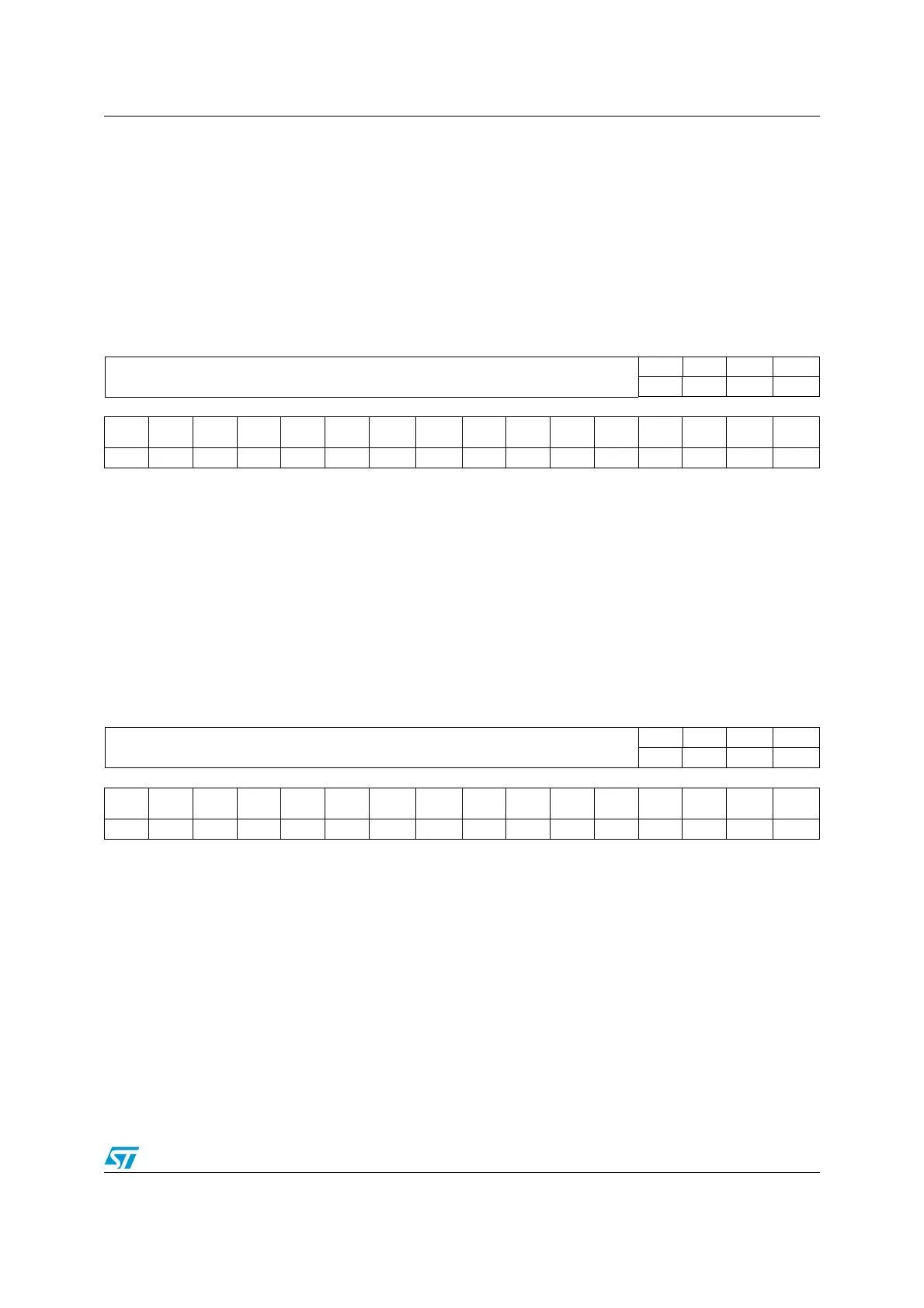

10.3.1 Interrupt mask register (EXTI_IMR)

Address offset: 0x00

Reset value: 0x0000 0000

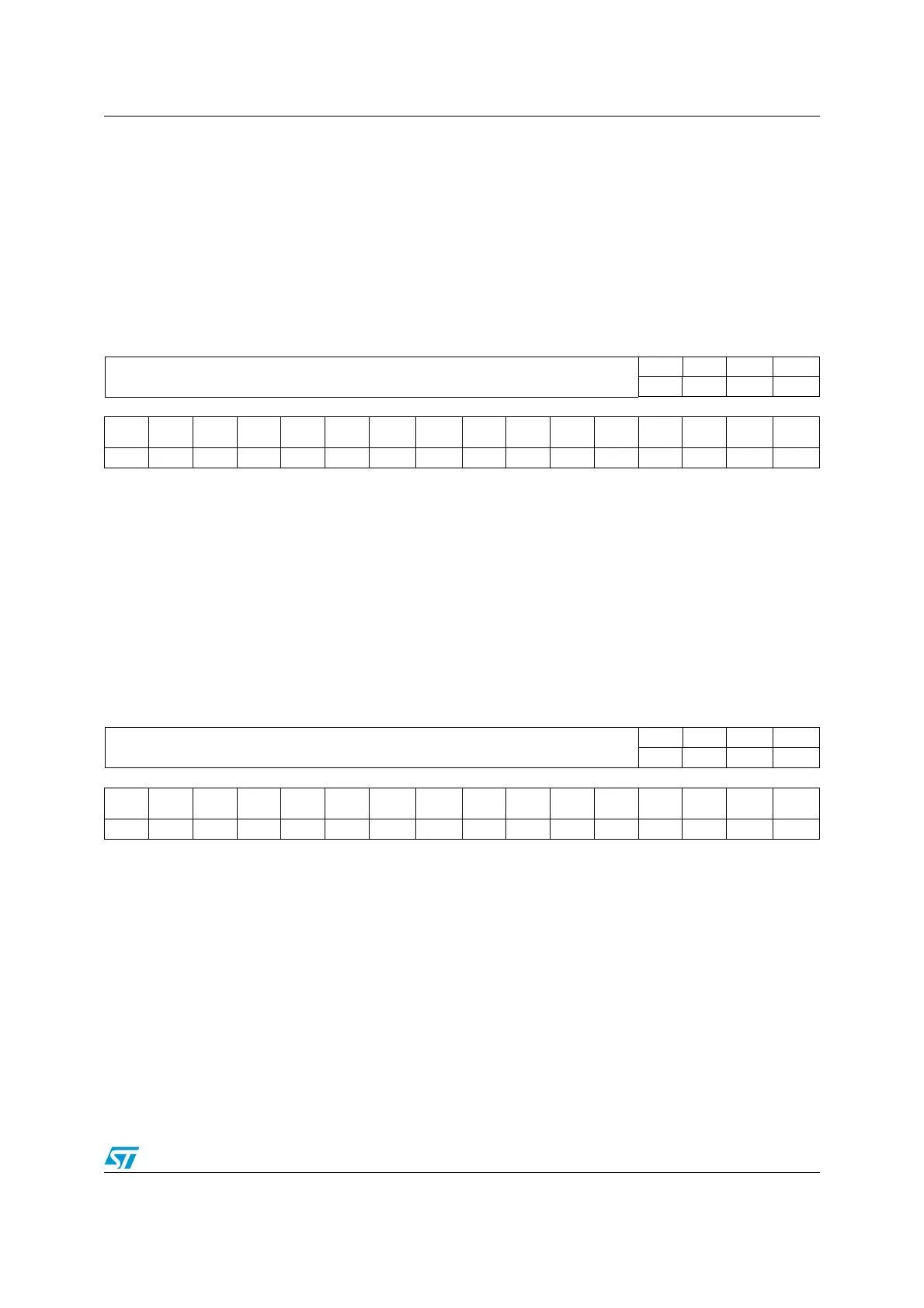

10.3.2 Event mask register (EXTI_EMR)

Address offset: 0x04

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

MR19 MR18 MR17 MR16

rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

MR15 MR14 MR13 MR12 MR11 MR10 MR9 MR8 MR7 MR6 MR5 MR4 MR3 MR2 MR1 MR0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:20 Reserved, must be kept at reset value (0).

Bits 19:0 MRx: Interrupt Mask on line x

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is not masked

Note: Bit 19 is used in connectivity line devices only and is reserved otherwise.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

MR19 MR18 MR17 MR16

rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

MR15 MR14 MR13 MR12 MR11 MR10 MR9 MR8 MR7 MR6 MR5 MR4 MR3 MR2 MR1 MR0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:20 Reserved, must be kept at reset value (0).

Bits 19:0 MRx: Event mask on line x

0: Event request from Line x is masked

1: Event request from Line x is not masked

Note: Bit 19 is used in connectivity line devices only and is reserved otherwise.

Loading...

Loading...