RM0008 Flexible static memory controller (FSMC)

Doc ID 13902 Rev 12 517/1096

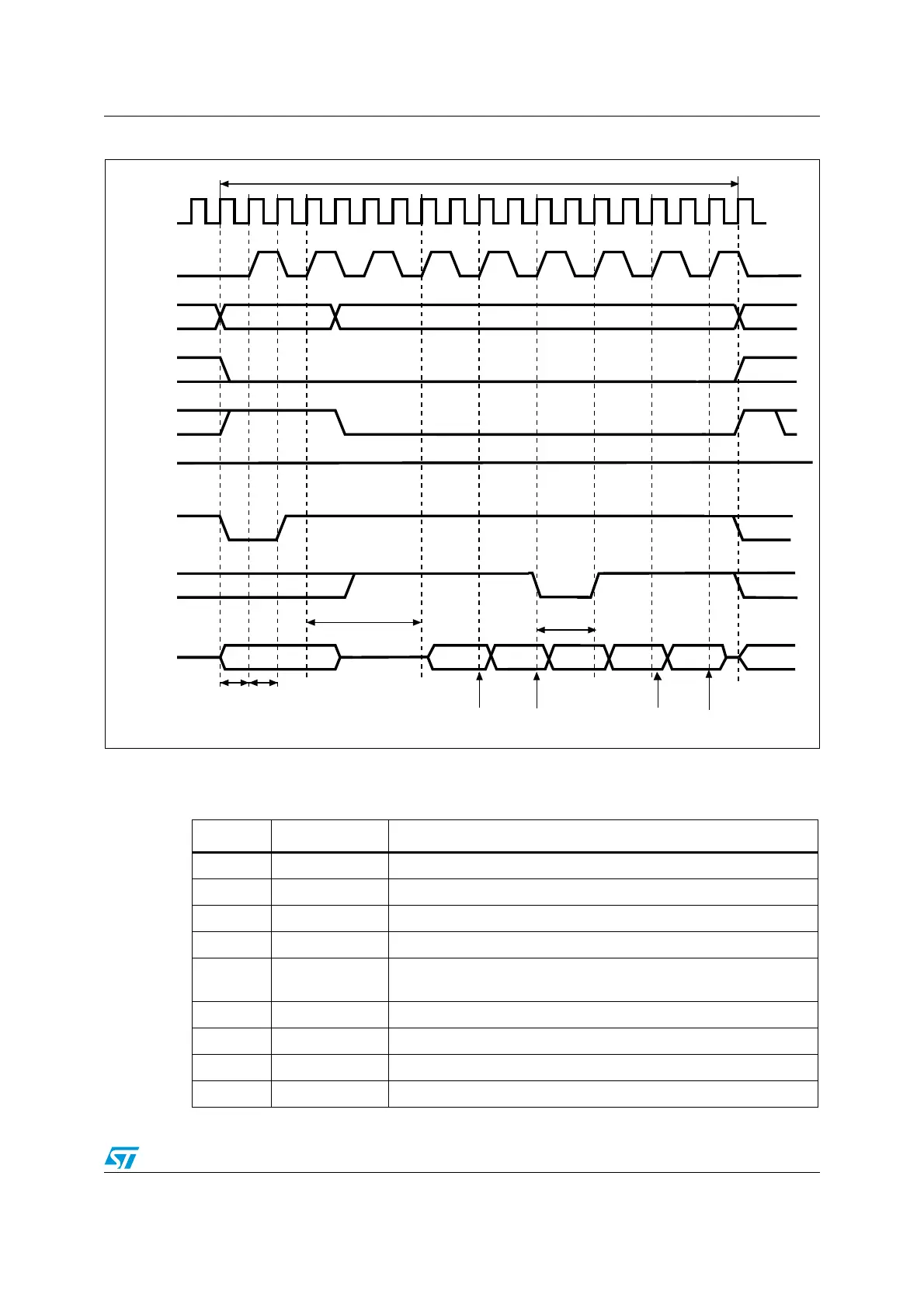

Figure 202. Synchronous multiplexed read mode - NOR, PSRAM (CRAM)

1. Byte lane outputs BL are not shown; for NOR access, they are held high, and, for PSRAM (CRAM) access, they are held

low.

!DDR;= DATA DATA

ADDR;=

-EMORYTRANSACTIONBURSTOFHALFWORDS

(#,+

#,+

!;=

.%X

./%

.7%

(IGH

.!$6

.7!)4

7!)4#&'

!$;=

CLOCK

CYCLE

CLOCK

CYCLE

$!4!,!4

INSERTEDWAITSTATE

$ATASTROBES

AIB

#,+CYCLES

DATA DATA

$ATASTROBES

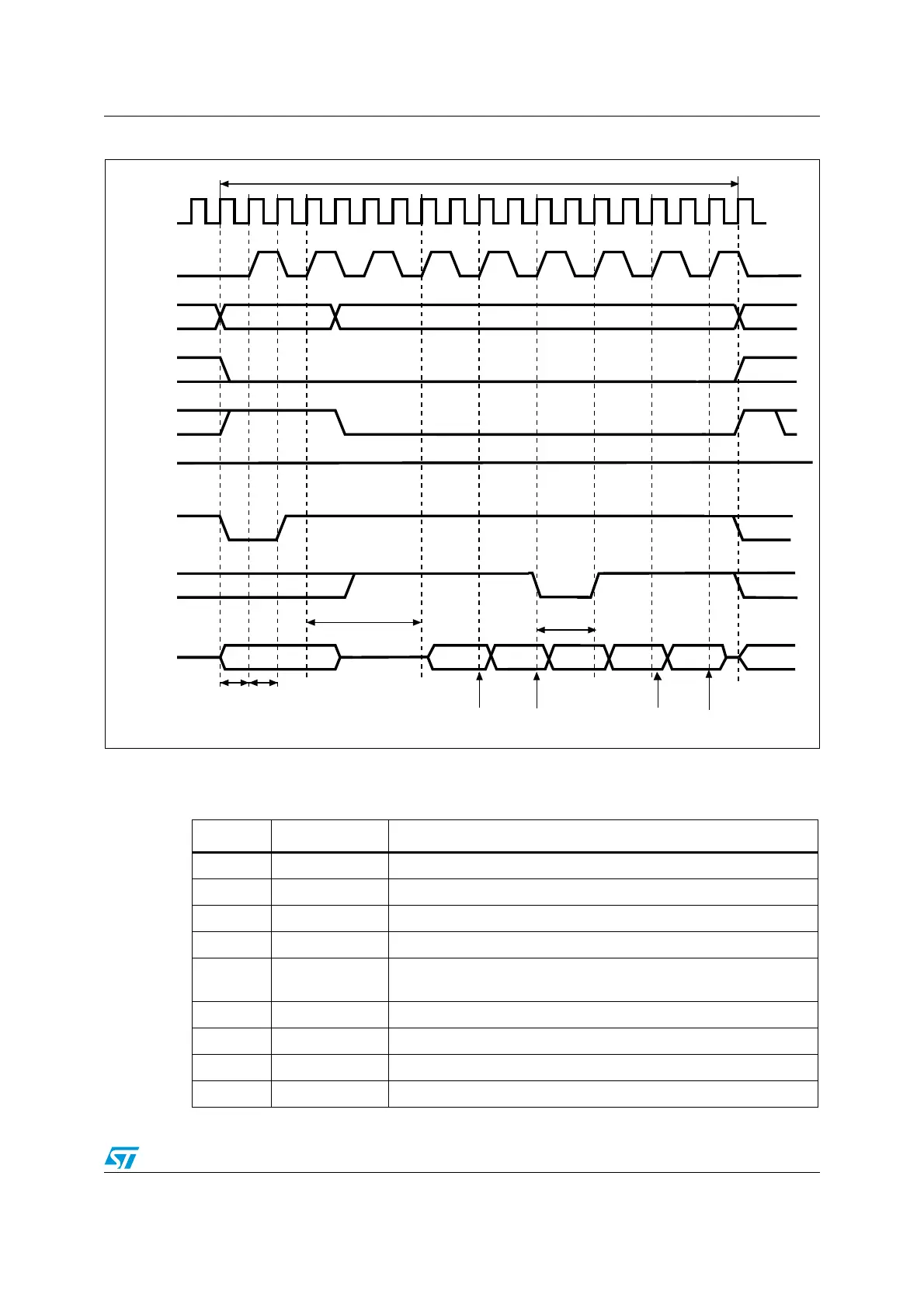

Table 124. FSMC_BCRx bit fields

Bit No. Bit name Value to set

31-20 0x0000

19 CBURSTRW No effect on synchronous read

18-15 0x0

14 EXTMOD 0x0

13 WAITEN

When high, the first data after latency period is taken as always

valid, regardless of the wait from memory value

12 WREN no effect on synchronous read

11 WAITCFG to be set according to memory

10 WRAPMOD no effect

9 WAITPOL to be set according to memory

Loading...

Loading...