USB on-the-go full-speed (OTG_FS) RM0008

902/1096 Doc ID 13902 Rev 12

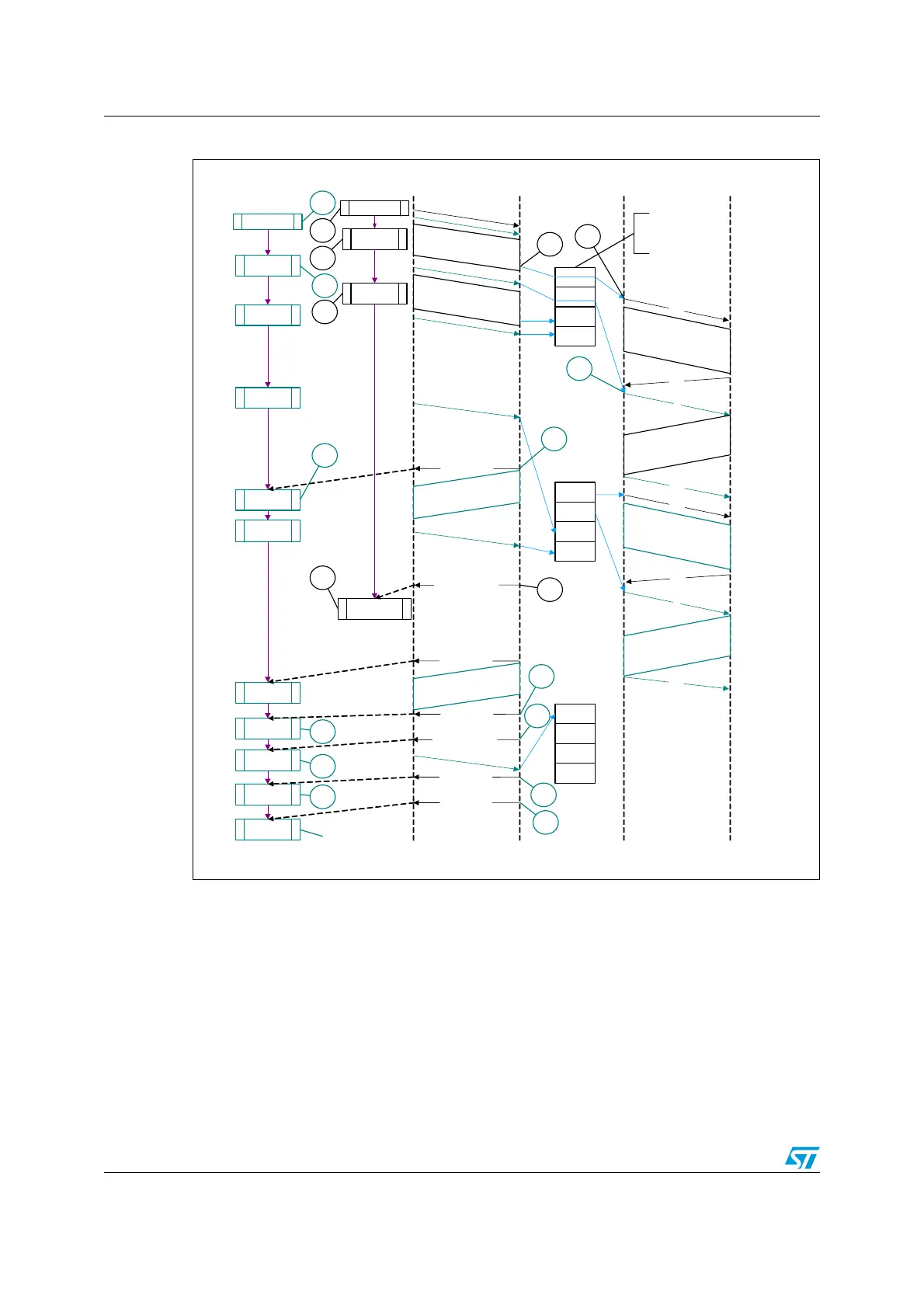

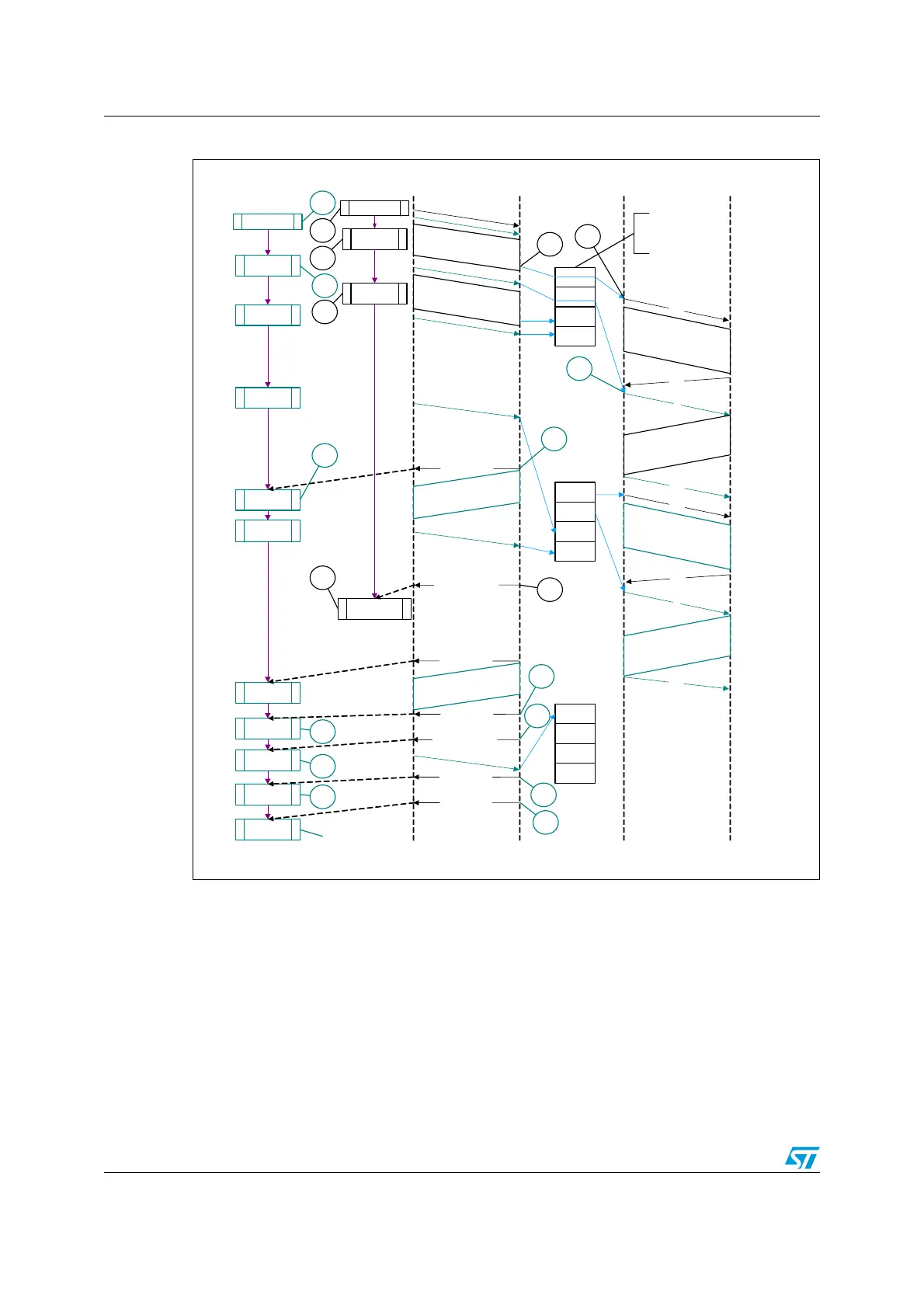

Figure 314. Bulk/control IN transactions

The sequence of operations is as follows:

a) Initialize channel 2.

b) Set the CHENA bit in HCCHAR2 to write an IN request to the non-periodic request

queue.

c) The core attempts to send an IN token after completing the current OUT

transaction.

d) The core generates an RXFLVL interrupt as soon as the received packet is written

to the receive FIFO.

e) In response to the RXFLVL interrupt, mask the RXFLVL interrupt and read the

received packet status to determine the number of bytes received, then read the

receive FIFO accordingly. Following this, unmask the RXFLVL interrupt.

A

C

K

HostApplication DeviceAHB USB

O

U

T

D

A

T

A

0

M

P

S

1

MPS

1

MPS

write_tx _fifo

(ch_1)

init_reg(ch_1)

set _ch_en

(ch_2)

init_reg(ch_2)

write_tx _fifo

(ch_1)

set _ch_en

(ch_2)

ch_2

ch_2

ch_1

ch_1

De-allocate

(ch_1)

I

N

ch_2

ch_2

ch_2

ch_1

A

C

K

O

U

T

set _ch_en

(ch_2)

Non-Periodic Request

Queu e

Assume that this queue

can hold 4 entries.

4

1

6

A

C

K

D

A

T

A

0

I

N

A

C

K

read_rx_sts

read_rx_fifo

1

MPS

set _ch_en

(ch_2)

1

MPS

read_rx_stsre

ad_rx_fifo

read_rx_sts

Disable

(ch_2)

1

2

3

4

5

6

7

De-allocate

(ch_2)

CHH interruptr

ch_2

2

3

5

7

8

9

12

13

read_rx_sts

10

11

D

A

T

A

1

M

P

S

D

A

T

A

1

ai15675

RXFLVL interrupt

XFRC interrupt

RXFLVL interrupt

RXFLVL interrupt

RXFLVL interrupt

XFRC interrupt

Loading...

Loading...