Debug support (DBG) RM0008

1066/1096 Doc ID 13902 Rev 12

Example of configuration

To output a simple value to the TPIU:

● Configure the TPIU and assign TRACE IOs by configuring the DBGMCU_CR (refer to

Section 31.17.2: TRACE pin assignment and Section 31.16.3: Debug MCU

configuration register)

● Write 0xC5ACCE55 to the ITM Lock Access Register to unlock the write access to the

ITM registers

● Write 0x00010005 to the ITM Trace Control Register to enable the ITM with Sync

enabled and an ATB ID different from 0x00

● Write 0x1 to the ITM Trace Enable Register to enable the Stimulus Port 0

● Write 0x1 to the ITM Trace Privilege Register to unmask stimulus ports 7:0

● Write the value to output in the Stimulus Port Register 0: this can be done by software

(using a printf function)

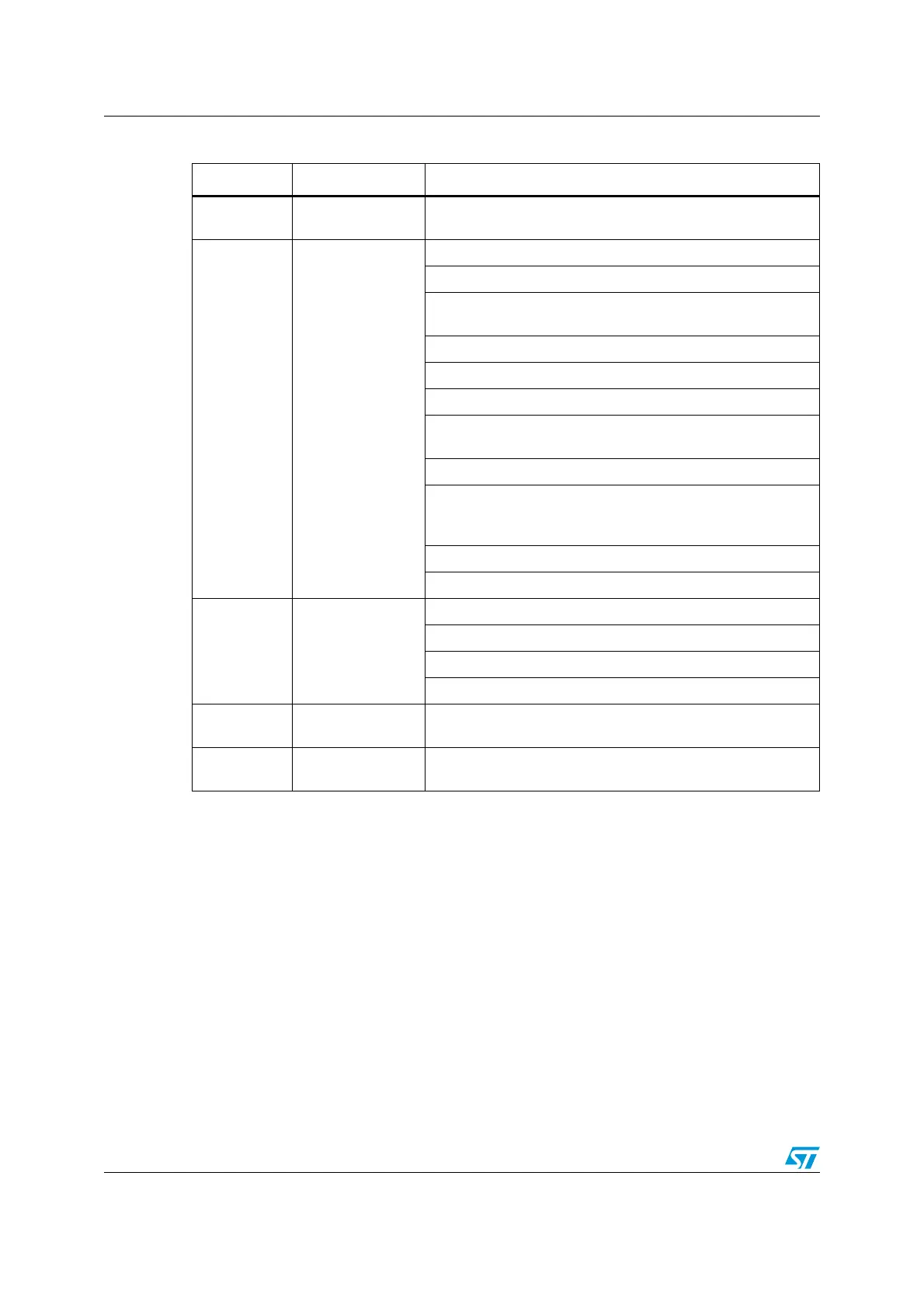

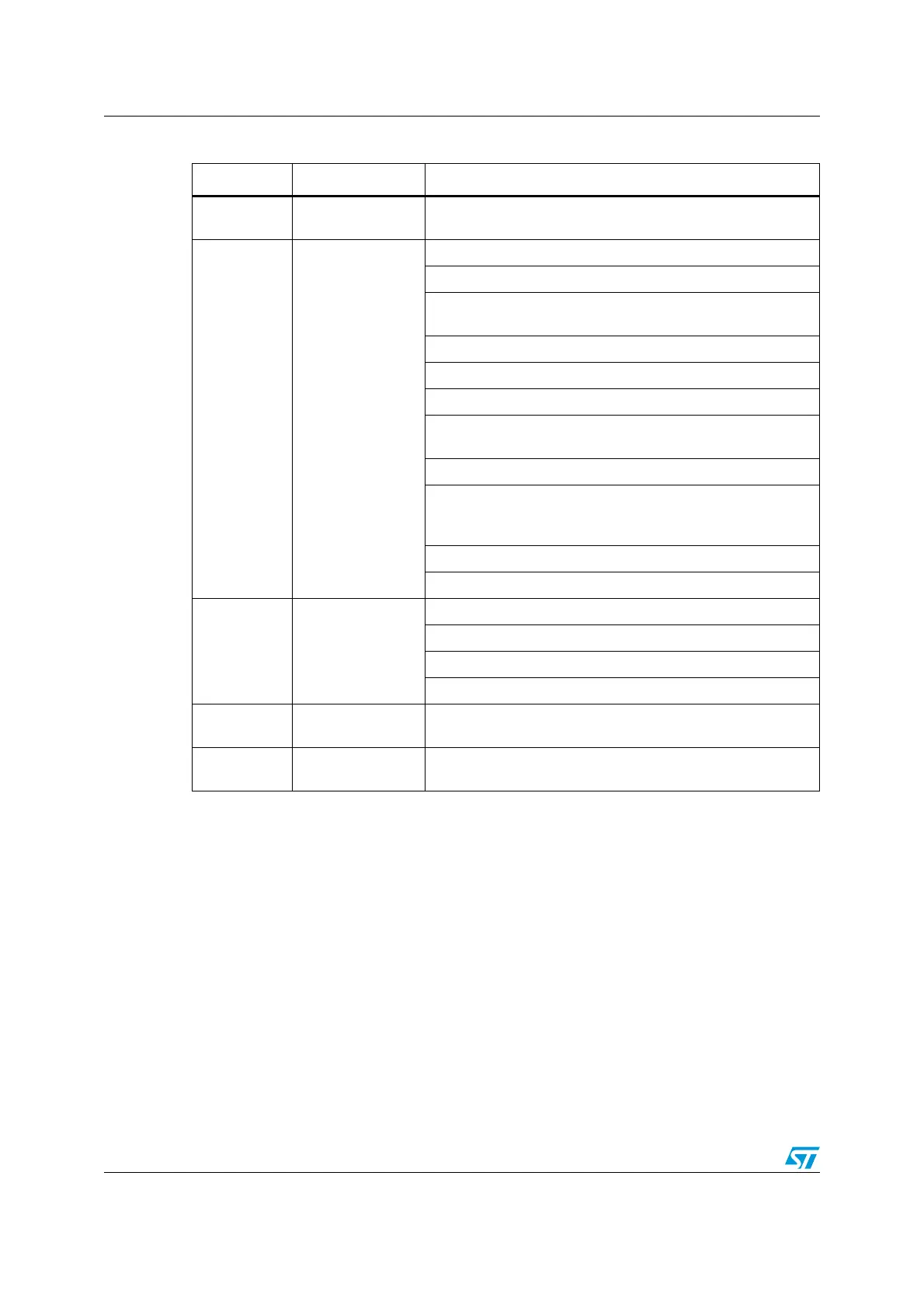

Table 225. Main ITM registers

Address Register Details

@E0000FB0 ITM lock access

Write 0xC5ACCE55 to unlock Write Access to the other ITM

registers

@E0000E80 ITM trace control

Bits 31-24 = Always 0

Bits 23 = Busy

Bits 22-16 = 7-bits ATB ID which identifies the source of the

trace data.

Bits 15-10 = Always 0

Bits 9:8 = TSPrescale = Time Stamp Prescaler

Bits 7-5 = Reserved

Bit 4 = SWOENA = Enable SWV behavior (to clock the

timestamp counter by the SWV clock).

Bit 3 = DWTENA: Enable the DWT Stimulus

Bit 2 = SYNCENA: this bit must be to 1 to enable the DWT to

generate synchronization triggers so that the TPIU can then

emit the synchronization packets.

Bit 1 = TSENA (Timestamp Enable)

Bit 0 = ITMENA: Global Enable Bit of the ITM

@E0000E40 ITM trace privilege

Bit 3: mask to enable tracing ports31:24

Bit 2: mask to enable tracing ports23:16

Bit 1: mask to enable tracing ports15:8

Bit 0: mask to enable tracing ports7:0

@E0000E00 ITM trace enable

Each bit enables the corresponding Stimulus port to generate

trace.

@E0000000-

E000007C

Stimulus port

registers 0-31

Write the 32-bits data on the selected Stimulus Port (32

available) to be traced out.

Loading...

Loading...