RM0008 Inter-integrated circuit (I

2

C) interface

Doc ID 13902 Rev 12 745/1096

26.3.8 Packet error checking

A PEC calculator has been implemented to improve the reliability of communication. The

PEC is calculated by using the C(x) = x

8

+ x

2

+ x + 1 CRC-8 polynomial serially on each bit.

● PEC calculation is enabled by setting the ENPEC bit in the I2C_CR1 register. PEC is a

CRC-8 calculated on all message bytes including addresses and R/W bits.

– In transmission: set the PEC transfer bit in the I2C_CR1 register after the TxE

event corresponding to the last byte. The PEC will be transferred after the last

transmitted byte.

– In reception: set the PEC bit in the I2C_CR1 register after the RxNE event

corresponding to the last byte so that the receiver sends a NACK if the next

received byte is not equal to the internally calculated PEC. In case of Master-

Receiver, a NACK must follow the PEC whatever the check result. The PEC must

be set before the ACK pulse of the current byte reception.

● A PECERR error flag/interrupt is also available in the I2C_SR1 register.

● If DMA and PEC calculation are both enabled:-

– In transmission: when the I

2

C interface receives an EOT signal from the DMA

controller, it automatically sends a PEC after the last byte.

– In reception: when the I

2

C interface receives an EOT_1 signal from the DMA

controller, it will automatically consider the next byte as a PEC and will check it. A

DMA request is generated after PEC reception.

● To allow intermediate PEC transfers, a control bit is available in the I2C_CR2 register

(LAST bit) to determine if it is really the last DMA transfer or not. If it is the last DMA

request for a master receiver, a NACK is automatically sent after the last received byte.

● PEC calculation is corrupted by an arbitration loss.

26.4 I

2

C interrupts

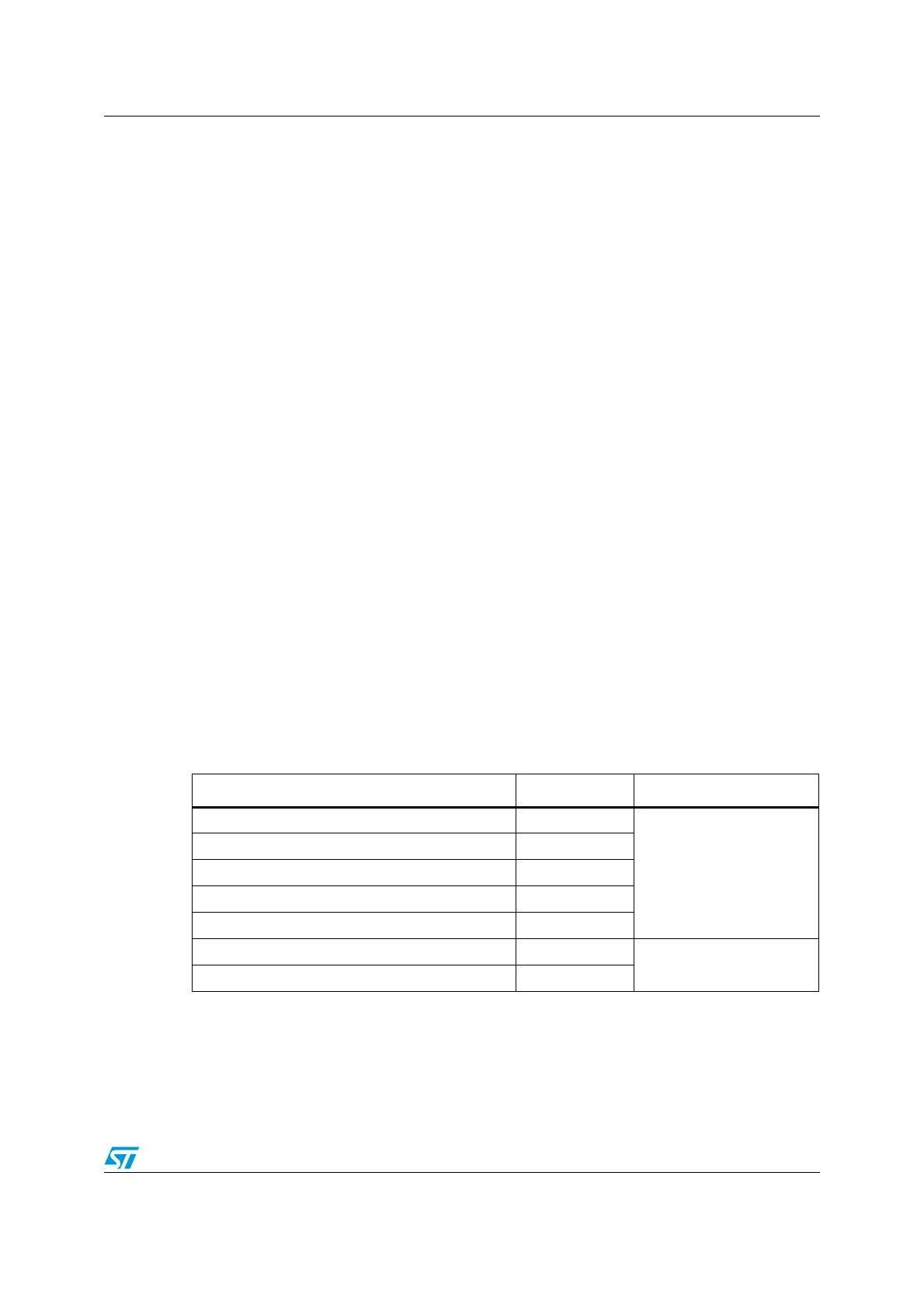

The table below gives the list of I

2

C interrupt requests.

Table 188. I

2

C Interrupt requests

Interrupt event Event flag Enable control bit

Start bit sent (Master) SB

ITEVFEN

Address sent (Master) or Address matched (Slave) ADDR

10-bit header sent (Master) ADD10

Stop received (Slave) STOPF

Data byte transfer finished BTF

Receive buffer not empty RxNE

ITEVFEN and ITBUFEN

Transmit buffer empty TxE

Loading...

Loading...