RM0008 Flexible static memory controller (FSMC)

Doc ID 13902 Rev 12 495/1096

21.5.1 External memory interface signals

Table 104, Table 105 and Table 106 list the signals that are typically used to interface NOR

Flash, SRAM and PSRAM.

Note: Prefix “N”. specifies the associated signal as active low.

NOR Flash, nonmultiplexed I/Os

NOR Flash memories are addressed in 16-bit words. The maximum capacity is 512 Mbit (26

address lines).

NOR Flash, multiplexed I/Os

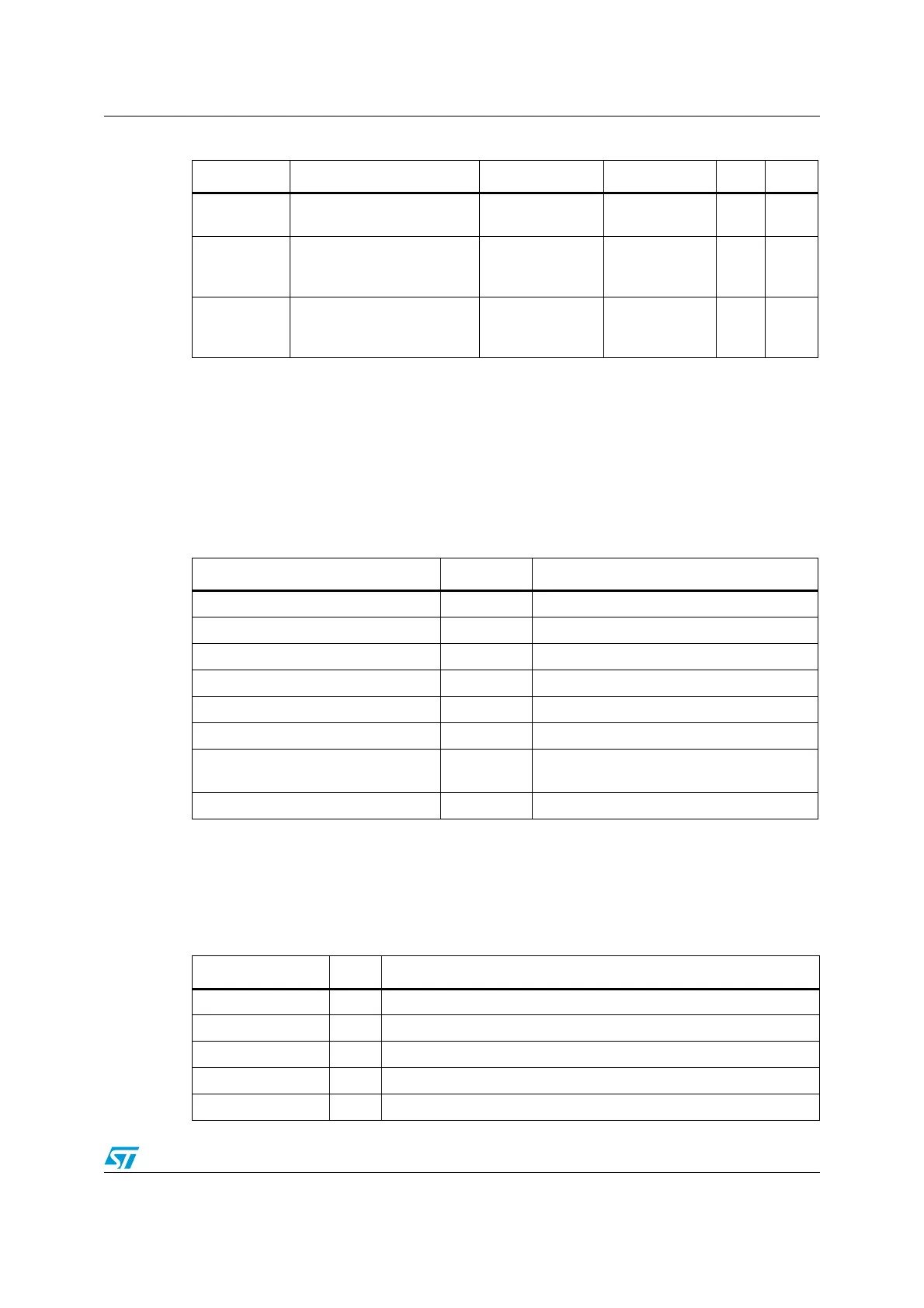

Bust turn

Duration of the bus

turnaround phase

Asynchronous and

synchronous read

AHB clock cycle

(HCLK)

116

Clock divide

ratio

Number of AHB clock cycles

(HCLK) to build one memory

clock cycle (CLK)

Synchronous

AHB clock cycle

(HCLK)

116

Data latency

Number of clock cycles to

issue to the memory before

the first data of the burst

Synchronous

Memory clock

cycle (CLK)

217

Table 103. Programmable NOR/PSRAM access parameters (continued)

Parameter Function Access mode Unit Min. Max.

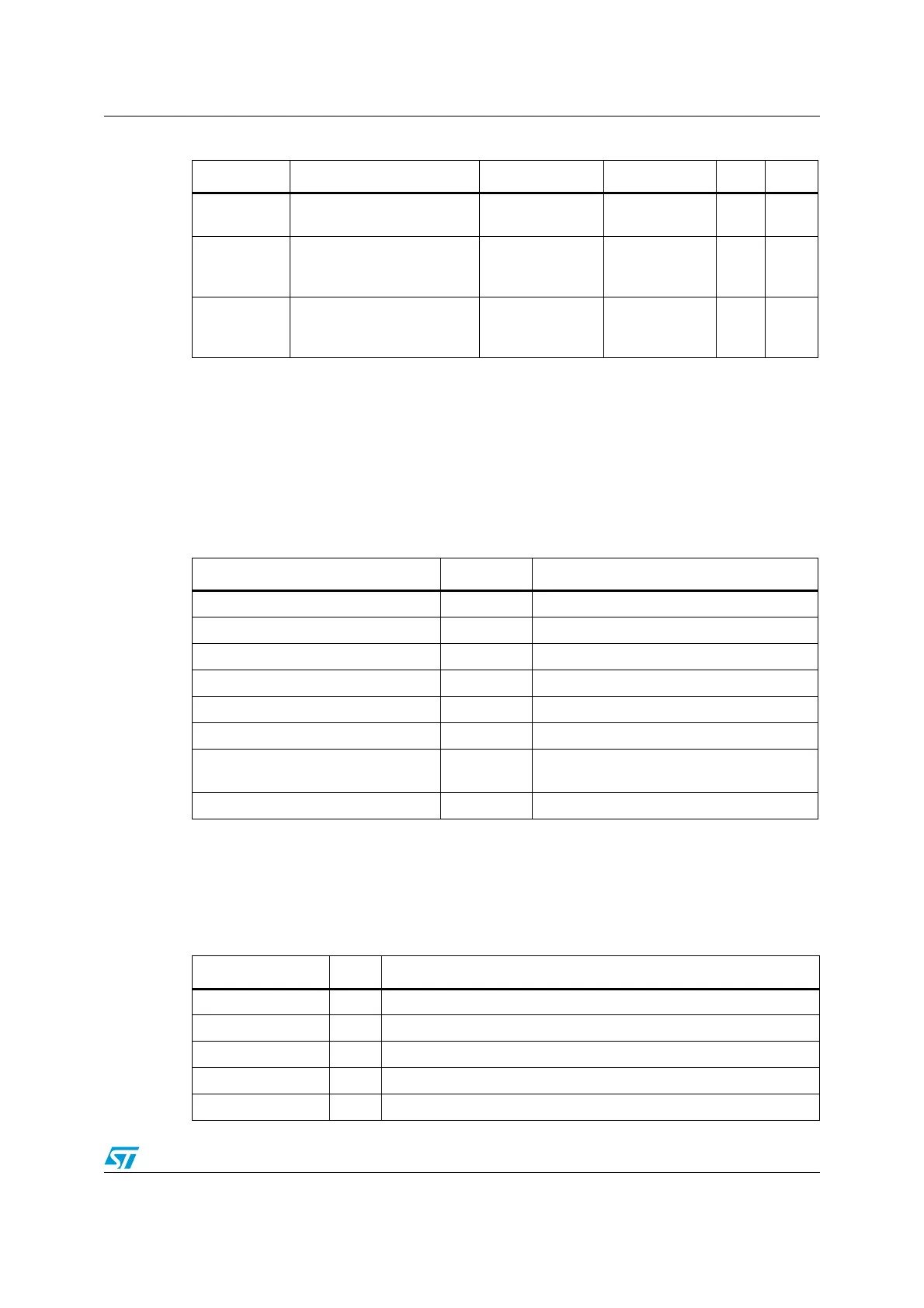

Table 104. Nonmuxed I/O NOR Flash

FSMC signal name I/O Function

CLK O Clock (for synchronous burst)

A[25:0] O Address bus

D[15:0] I/O Bidirectional data bus

NE[x] O Chip select, x = 1..4

NOE O Output enable

NWE O Write enable

NL(=NADV) O

Latch enable (this signal is called address

valid, NADV, by some NOR Flash devices)

NWAIT I NOR Flash wait input signal to the FSMC

Table 105. Muxed I/O NOR Flash

FSMC signal name I/O Function

CLK O Clock (for synchronous burst)

A[25:16] O Address bus

AD[15:0] I/O 16-bit multiplexed, bidirectional address/data bus

NE[x] O Chip select, x = 1..4

NOE O Output enable

Loading...

Loading...