Serial peripheral interface (SPI) RM0008

688/1096 Doc ID 13902 Rev 12

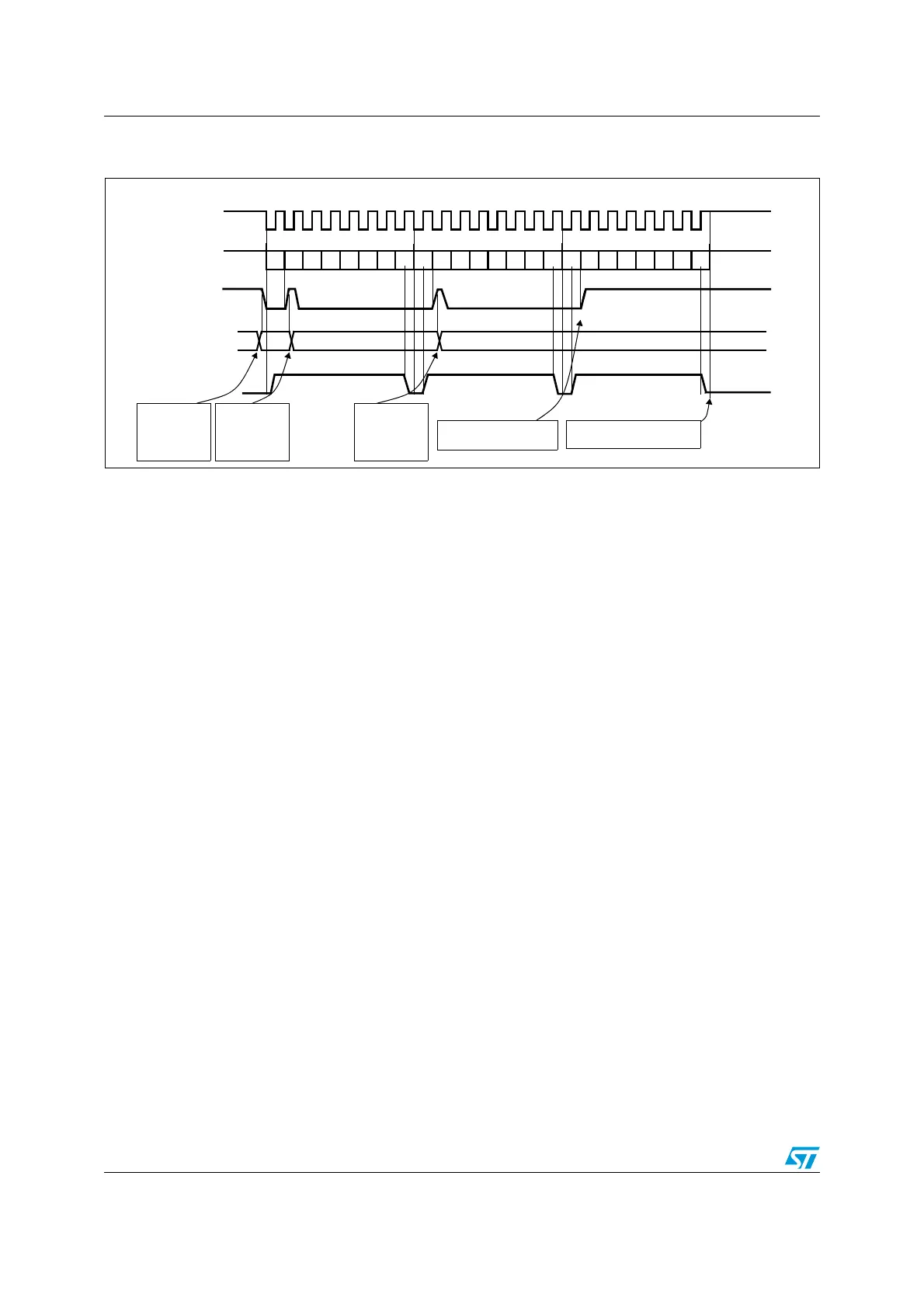

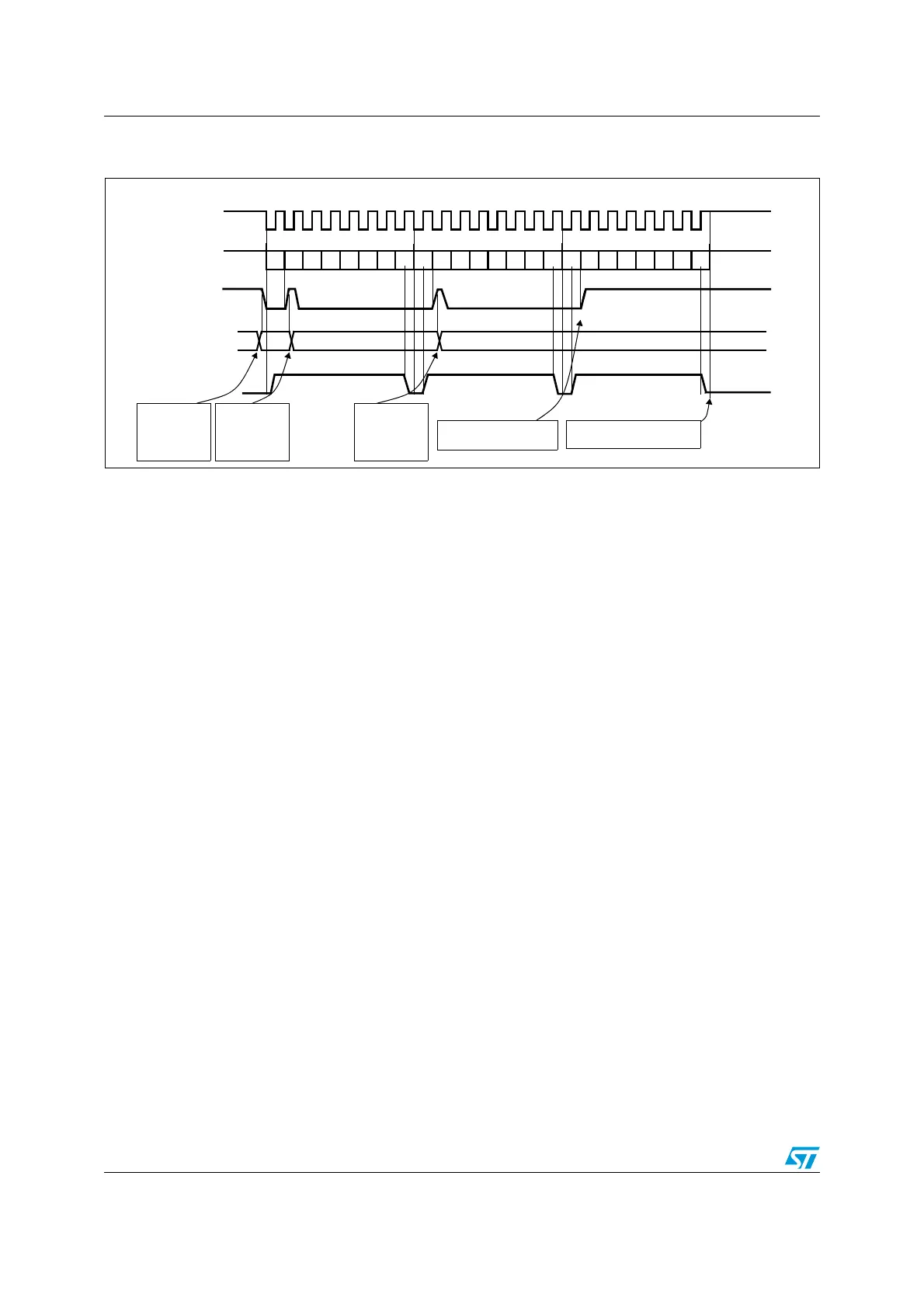

Figure 243. TXE/BSY in Slave transmit-only mode (BIDIMODE=0 and RXONLY=0) in the case of

continuous transfers

Bidirectional transmit procedure (BIDIMODE=1 and BIDIOE=1)

In this mode, the procedure is similar to the procedure in Transmit-only mode except that the

BIDIMODE and BIDIOE bits both have to be set in the SPI_CR2 register before enabling the

SPI.

Unidirectional receive-only procedure (BIDIMODE=0 and RXONLY=1)

In this mode, the procedure can be reduced as described below (see Figure 244):

1. Set the RXONLY bit in the SPI_CR2 register.

2. Enable the SPI by setting the SPE bit to 1:

a) In master mode, this immediately activates the generation of the SCK clock, and

data are serially received until the SPI is disabled (SPE=0).

b) In slave mode, data are received when the SPI master device drives NSS low and

generates the SCK clock.

3. Wait until RXNE=1 and read the SPI_DR register to get the received data (this clears

the RXNE bit). Repeat this operation for each data item to be received.

This procedure can also be implemented using dedicated interrupt subroutines launched at

each rising edge of the RXNE flag.

Note: If it is required to disable the SPI after the last transfer, follow the recommendation described

in Section 25.3.8: Disabling the SPI on page 693.

0xF1

Tx buffer

TXE flag

0xF2

BSY flag

0xF3

software writes

0xF1 into

SPI_DR

software waits

until TXE=1 and

writes 0xF2 into

SPI_DR

set by hardware

cleared by software

set by hardware

cleared by software

set by hardware

set by hardware

SCK

reset by hardware

Example in slave mode with CPOL=1, CPHA=1

(write to SPI_DR)

MISO/MOSI (out)

DATA 1 = 0xF1 DATA 2 = 0xF2

DATA 3 = 0xF3

software waits

until TXE=1 and

writes 0xF3 into

SPI_DR

software waits until BSY=0software waits until TXE=1

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

ai17346

Loading...

Loading...