Ethernet (ETH): media access control (MAC) with DMA controller RM0008

942/1096 Doc ID 13902 Rev 12

29.4 Ethernet functional description: SMI, MII and RMII

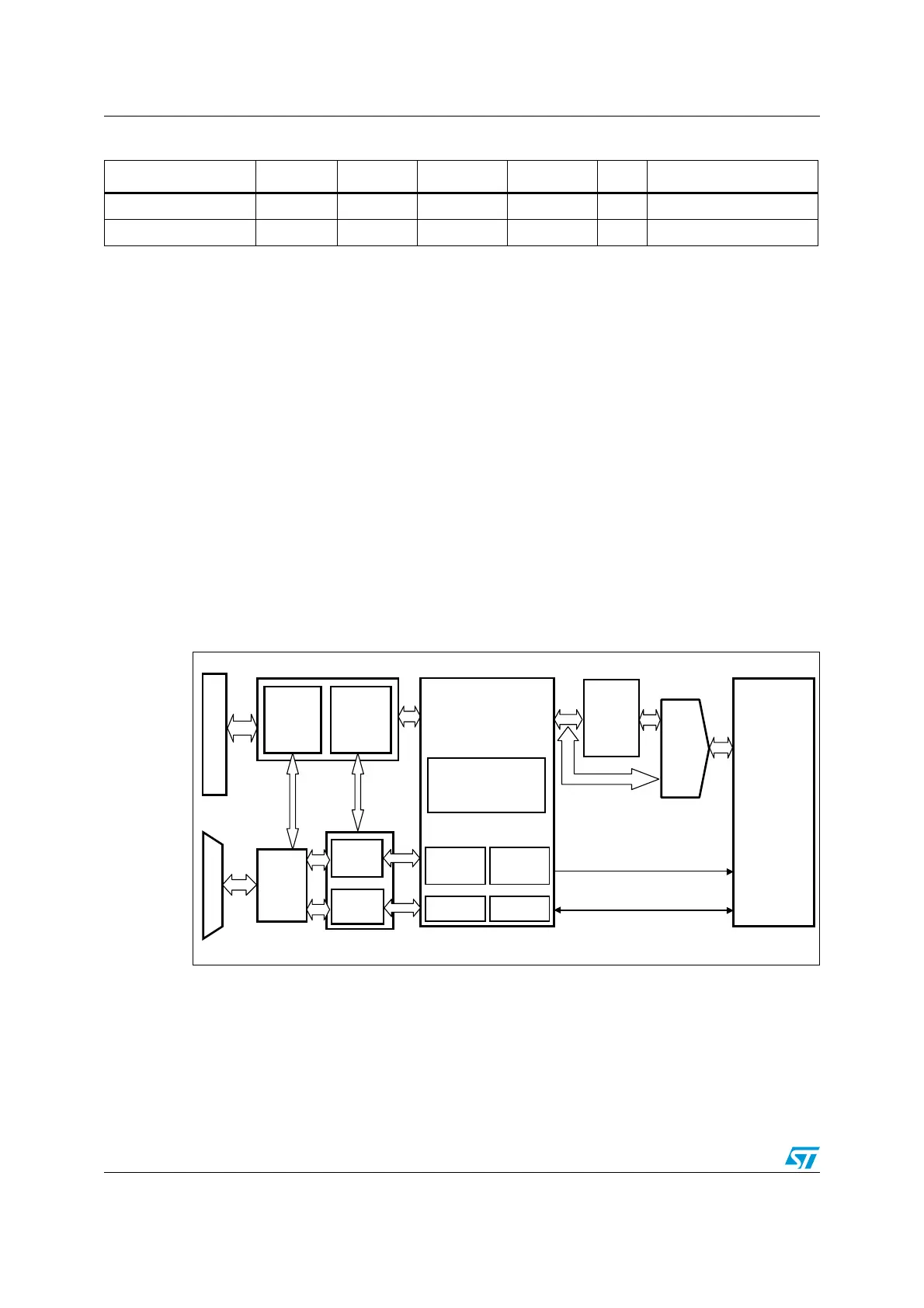

The Ethernet peripheral consists of a MAC 802.3 (media access control) with a dedicated

DMA controller. It supports both default media-independent interface (MII) and reduced

media-independent interface (RMII) through one selection bit (refer to AFIO_MAPR

register).

The DMA controller interfaces with the Core and memories through the AHB Master and

Slave interfaces. The AHB Master Interface controls data transfers while the AHB Slave

interface accesses Control and Status Registers (CSR) space.

The Transmit FIFO (Tx FIFO) buffers data read from system memory by the DMA before

transmission by the MAC Core. Similarly, the Receive FIFO (Rx FIFO) stores the Ethernet

frames received from the line until they are transferred to system memory by the DMA.

The Ethernet peripheral also includes an SMI to communicate with external PHY. A set of

configuration registers permit the user to select the wanted mode and features for the MAC

and the DMA controller.

Note: The AHB clock frequency must be at least 25 MHz when the Ethernet is used.

Figure 325. ETH block diagram

1. For AHB connections please refer to Figure 1: System architecture.

29.4.1 Station management interface: SMI

The station management interface (SMI) allows the application to access any PHY registers

through a 2-wire clock and data lines. The interface supports accessing up to 32 PHYs.

ETH_MII_RXD2 - RXD2 - - PD11 Floating input (reset state)

ETH_MII_RXD3 - RXD3 - - PD12 Floating input (reset state)

Table 205. Ethernet pin configuration (continued)

MAC signals MII default MII remap RMII default RMII remap Pin Pin configuration

+BYTE

28&)&/

%THERNET

$-!

-EDIAACCESS

CONTROL

-!#

-!#

CONTROL

REGISTERS

$-!

CONTROL

STATUS

REGISTERS

/PERATION

MODE

REGISTER

)NTERFACE

3ELECT

-))

-$#

-$)/

!("3LAVEINTERFACE

2-))

AIC

"USMATRIX

%XTERNAL0(9

#HECKSUM

OFFLOAD

040

)%%%

0-4 --#

+BYTE

48&)&/

Loading...

Loading...