RM0008 Digital-to-analog converter (DAC)

Doc ID 13902 Rev 12 247/1096

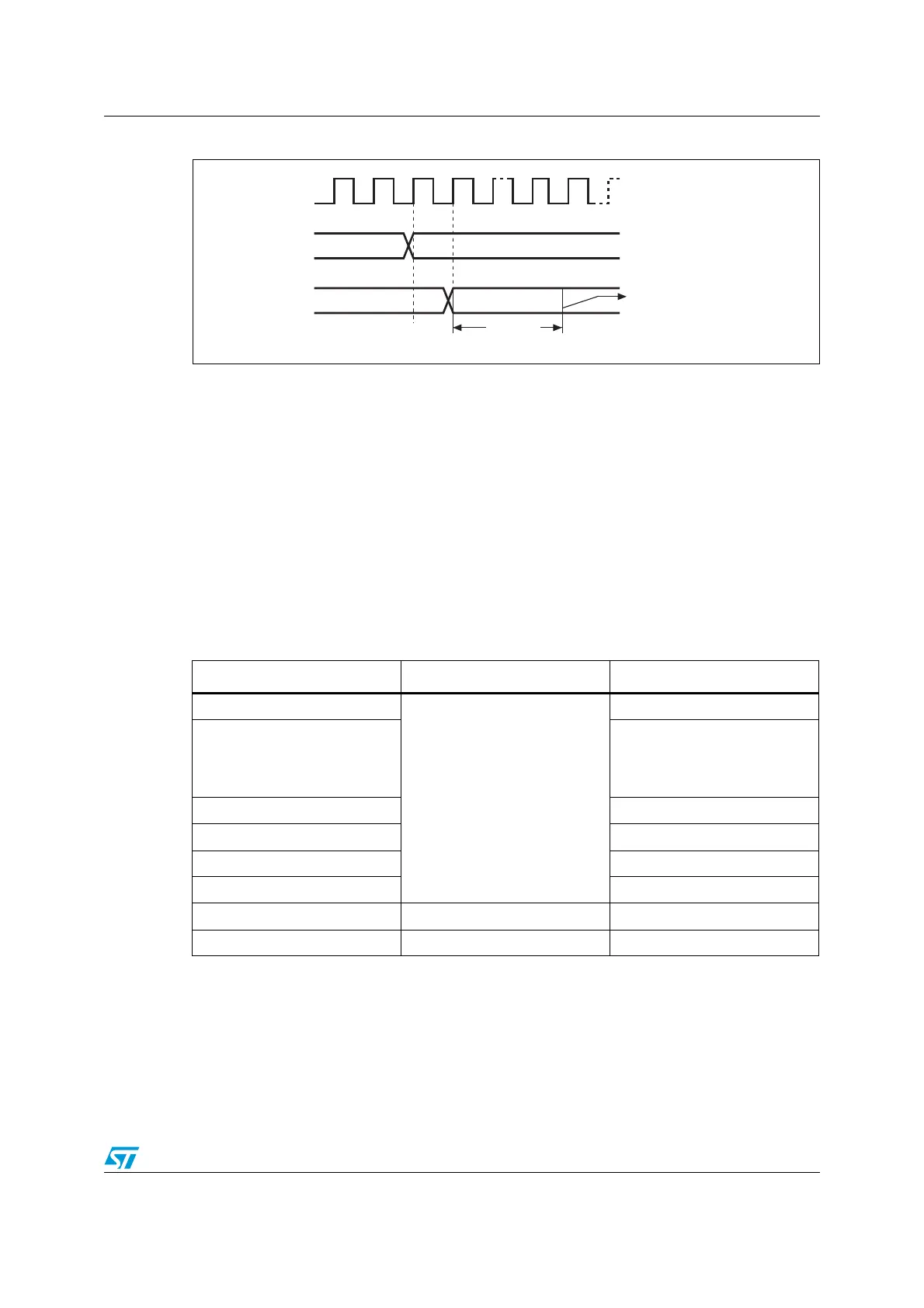

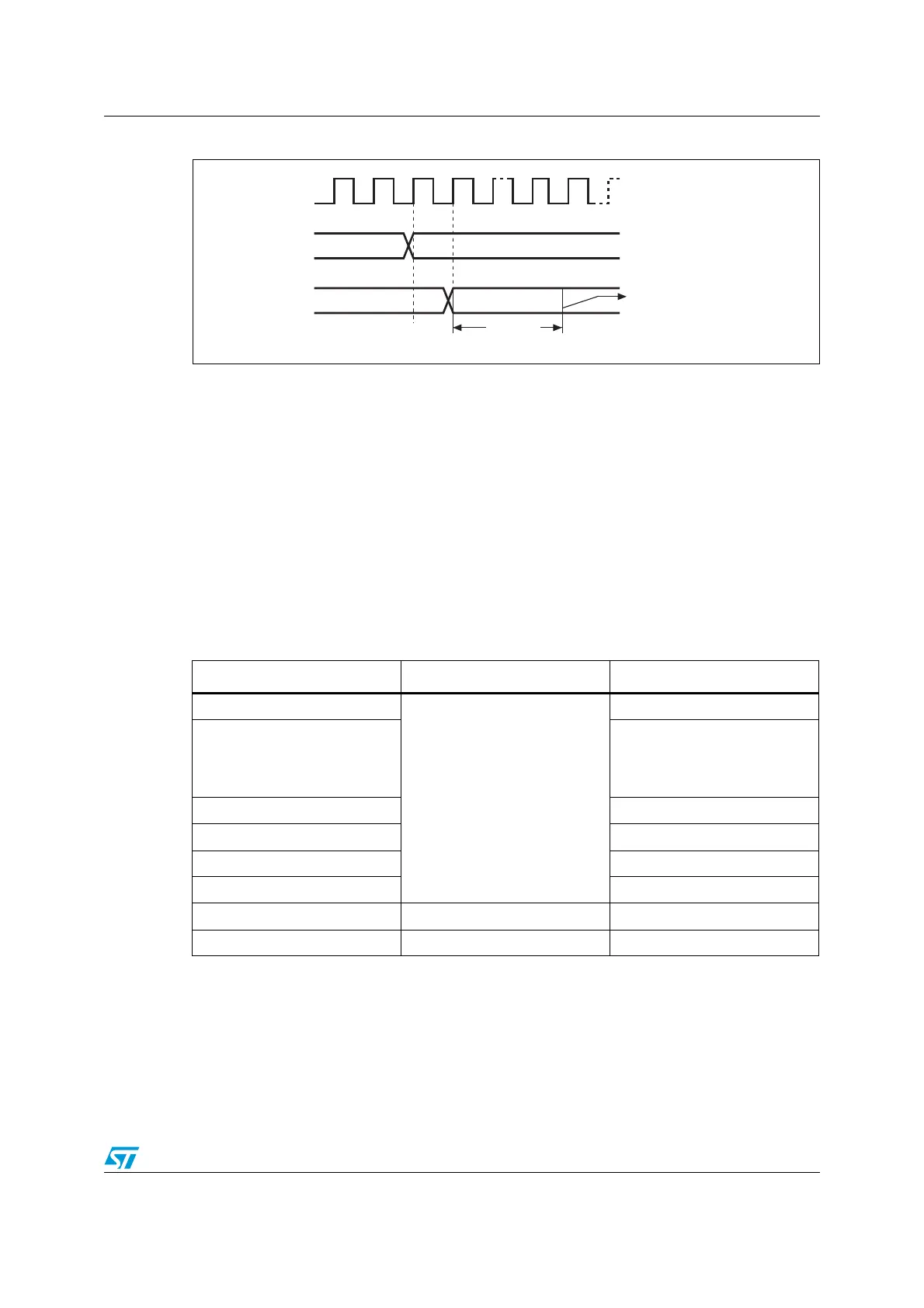

Figure 43. Timing diagram for conversion with trigger disabled TEN = 0

12.3.5 DAC output voltage

Digital inputs are converted to output voltages on a linear conversion between 0 and V

REF+

.

The analog output voltages on each DAC channel pin are determined by the following

equation:

12.3.6 DAC trigger selection

If the TENx control bit is set, conversion can then be triggered by an external event (timer

counter, external interrupt line). The TSELx[2:0] control bits determine which out of 8 possi-

ble events will trigger conversion as shown in Table 74.

Each time a DAC interface detects a rising edge on the selected timer TRGO output, or on

the selected external interrupt line 9, the last data stored into the DAC_DHRx register is

transferred into the DAC_DORx register. The DAC_DORx register is updated three APB1

cycles after the trigger occurs.

If the software trigger is selected, the conversion starts once the SWTRIG bit is set.

SWTRIG is reset by hardware once the DAC_DORx register has been loaded with the

DAC_DHRx register contents.

APB1_CLK

0x1AC

0x1AC

t

SETTLING

DHR

DOR

Output voltage

available on DAC_OUT pin

ai14711b

DACoutput V

REF

DOR

4095

------------- -

×=

Table 74. External triggers

Source Type TSEL[2:0]

Timer 6 TRGO event

Internal signal from on-chip

timers

000

Timer 3 TRGO event in

connectivity line devices or

Timer 8 TRGO in high-density

and XL-density devices

001

Timer 7 TRGO event 010

Timer 5 TRGO event 011

Timer 2 TRGO event 100

Timer 4 TRGO event 101

EXTI line9 External pin 110

SWTRIG Software control bit 111

Loading...

Loading...