General-purpose timers (TIM2 to TIM5) RM0008

364/1096 Doc ID 13902 Rev 12

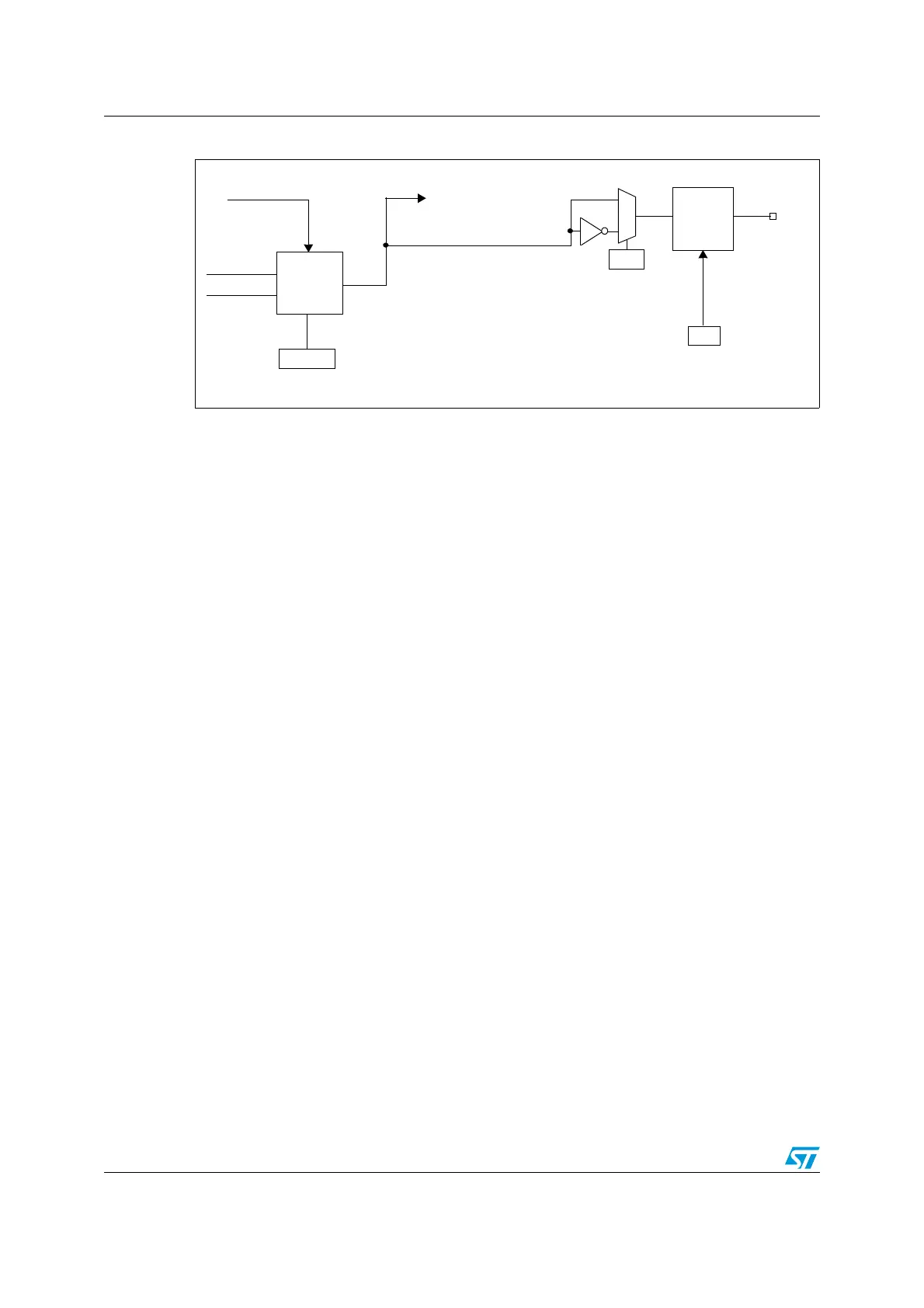

Figure 127. Output stage of capture/compare channel (channel 1)

The capture/compare block is made of one preload register and one shadow register. Write

and read always access the preload register.

In capture mode, captures are actually done in the shadow register, which is copied into the

preload register.

In compare mode, the content of the preload register is copied into the shadow register

which is compared to the counter.

Output mode

CNT > CCR1

CNT = CCR1

controller

TIMx_CCMR1

OC1M[2:0]

oc1ref

0

1

CC1P

TIMx_CCER

Output

Enable

Circuit

OC1

CC1E

TIMx_CCER

To the master mode

controller

ETRF

Loading...

Loading...