Flexible static memory controller (FSMC) RM0008

520/1096 Doc ID 13902 Rev 12

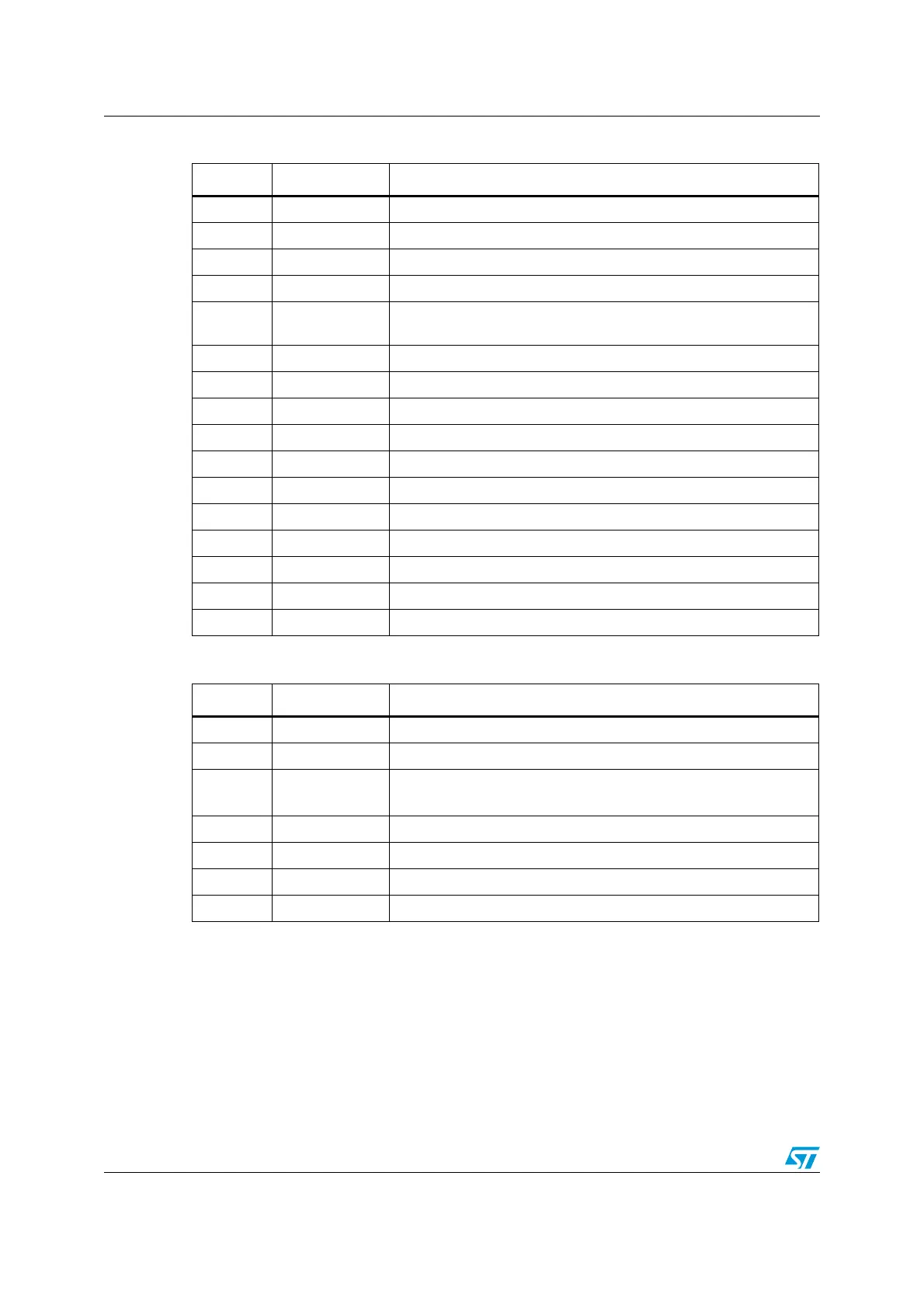

Table 126. FSMC_BCRx bit fields

Bit No. Bit name Value to set

31-20 0x0000

19 CBURSTRW 0x1

18-15 0x0

14 EXTMOD 0x0

13 WAITEN

When high, the first data after latency period is taken as always

valid, regardless of the wait from memory value

12 WREN no effect on synchronous read

11 WAITCFG 0x0

10 WRAPMOD no effect

9 WAITPOL to be set according to memory

8 BURSTEN no effect on synchronous write

7 FWPRLVL Set to protect memory from accidental writes

6 FACCEN Set according to memory support

5-4 MWID As needed

3-2 MTYP 0x1

1 MUXEN As needed

0 MBKEN 0x1

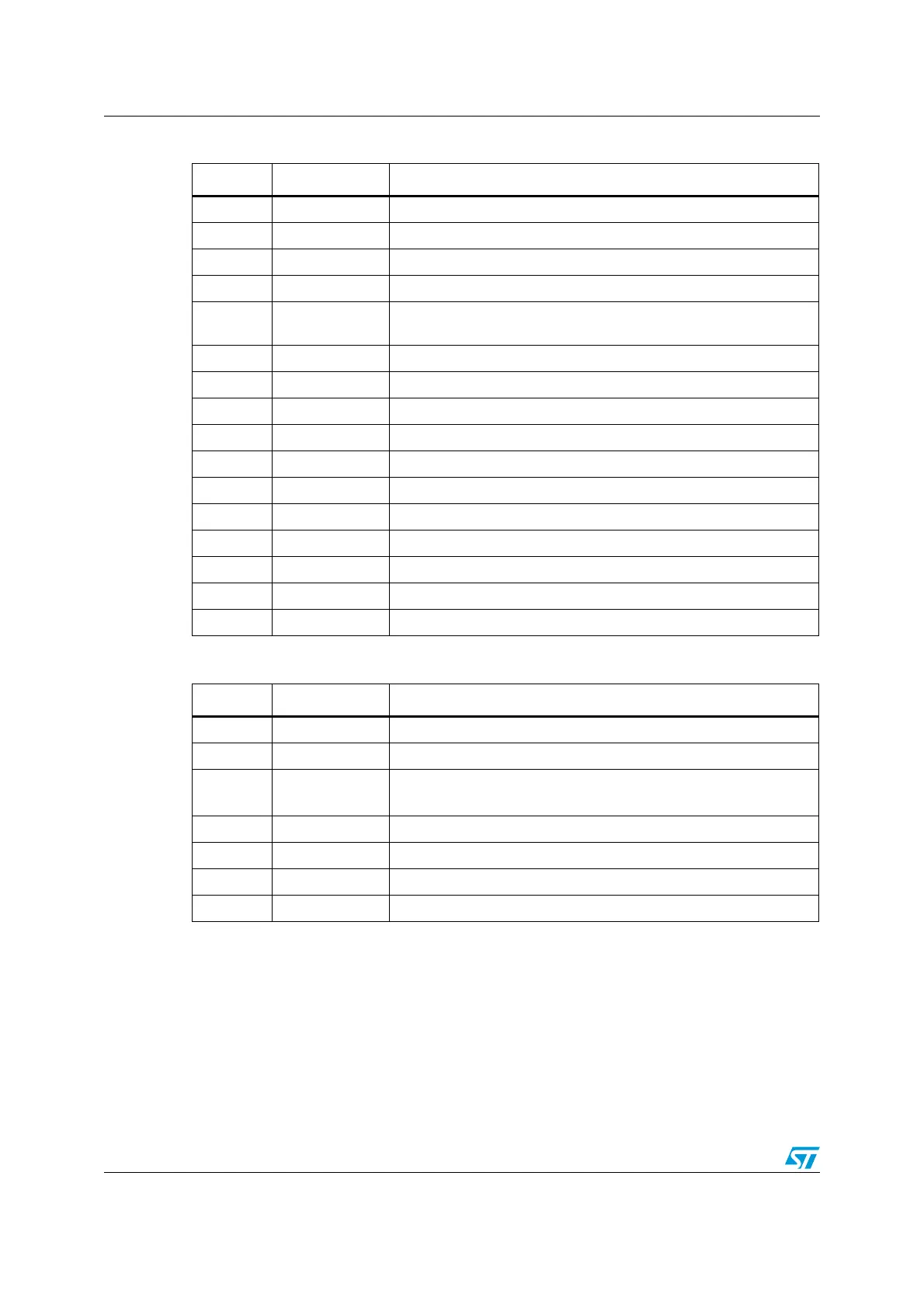

Table 127. FSMC_BTRx bit fields

Bit No. Bit name Value to set

31-30 - 0x0

27-24 DATLAT Data latency

23-20 CLKDIV

0 to get CLK = HCLK (not supported)

1 to get CLK = 2 × HCLK

19-16 BUSTURN No effect

15-8 DATAST No effect

7-4 ADDHLD No effect

3-0 ADDSET No effect

Loading...

Loading...