Inter-integrated circuit (I

2

C) interface RM0008

738/1096 Doc ID 13902 Rev 12

The procedure described above is valid for N>2. The cases where a single byte or two bytes

are to be received should be handled differently, as described below:

● Case of a single byte to be received:

– In the ADDR event, clear the ACK bit.

– Clear ADDR

– Program the STOP/START bit.

– Read the data after the RxNE flag is set.

● Case of two bytes to be received:

– Set POS and ACK

– Wait for the ADDR flag to be set

– Clear ADDR

–Clear ACK

– Wait for BTF to be set

–Program STOP

– Read DR twice

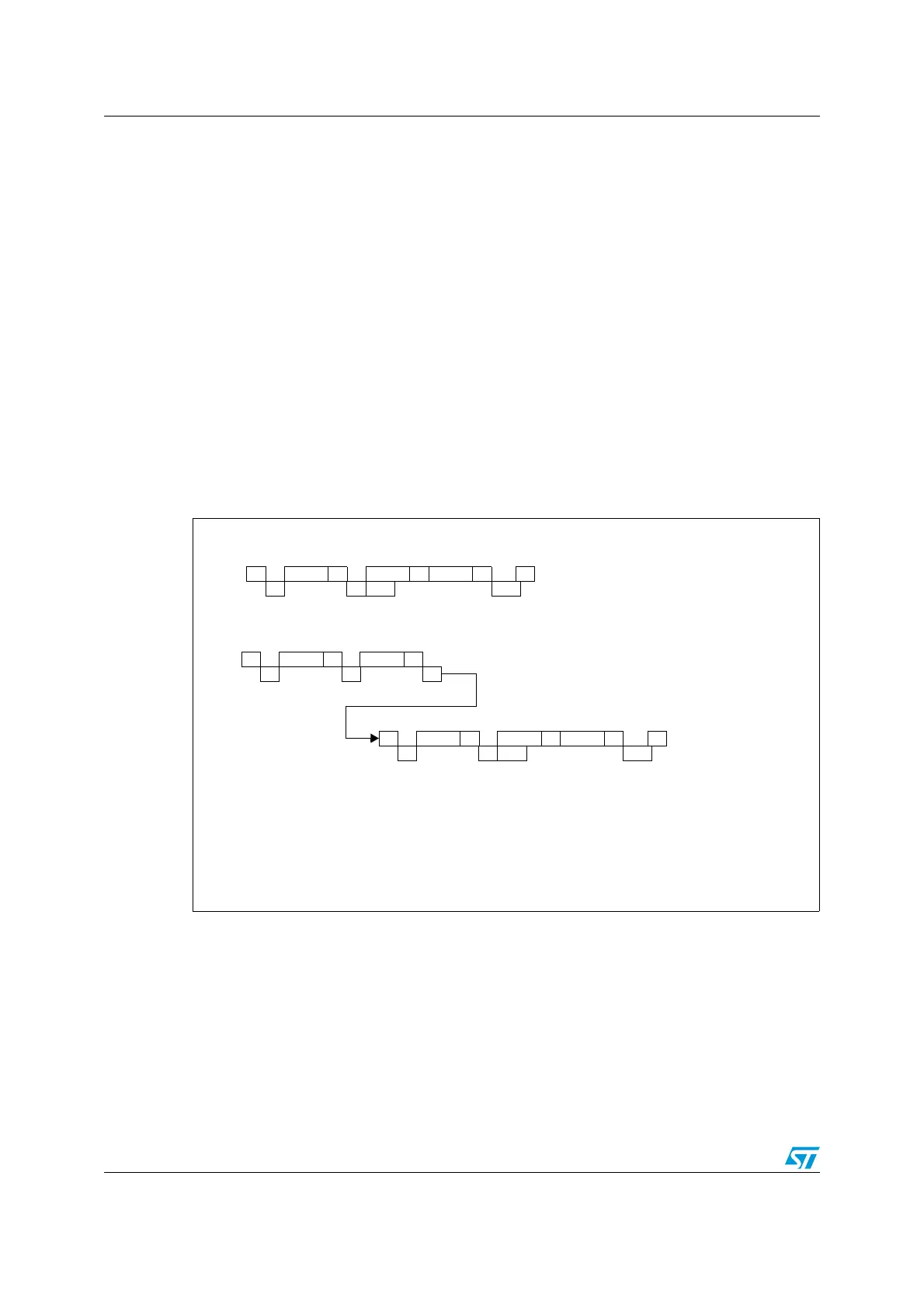

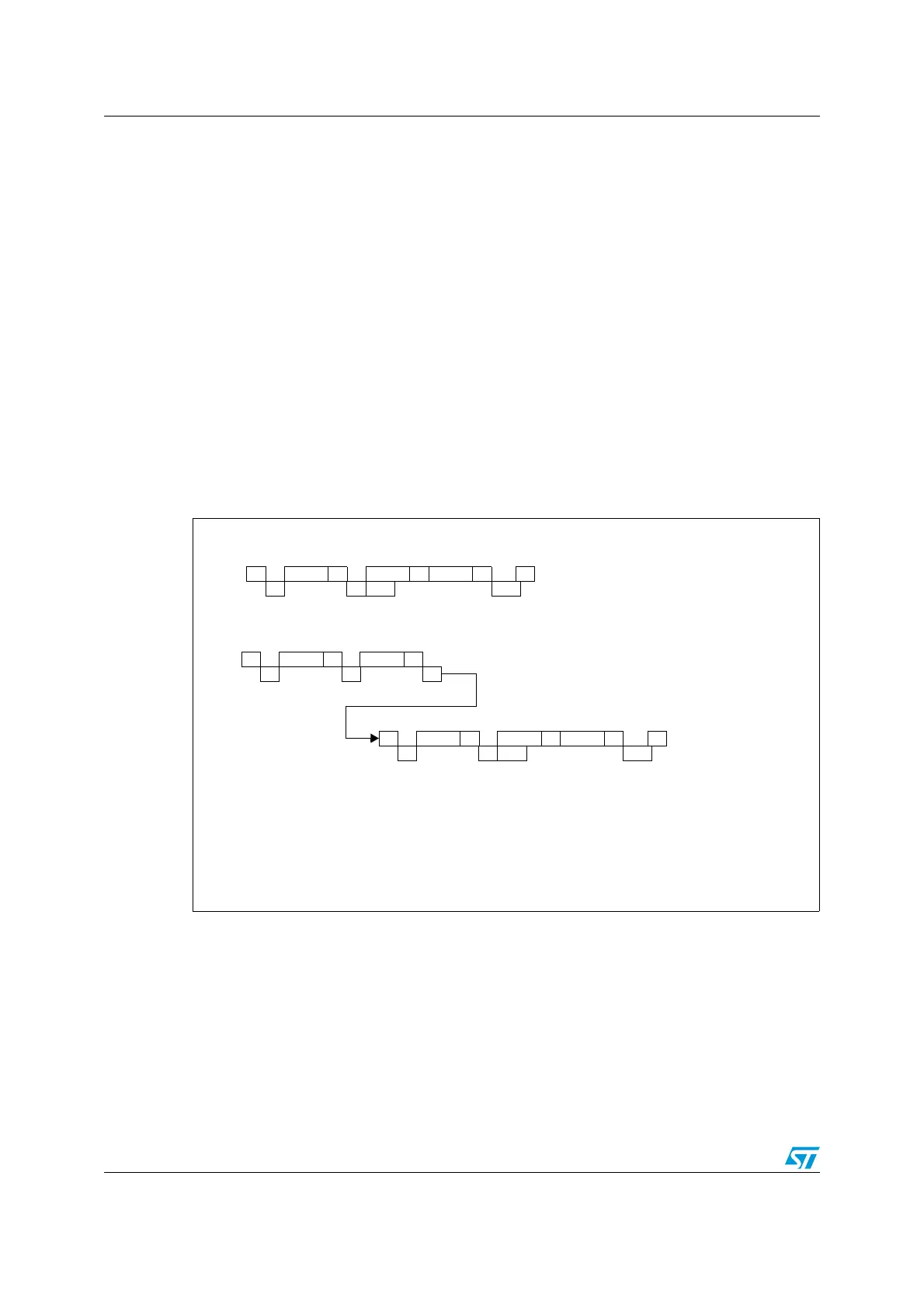

Figure 275. Method 2: transfer sequence diagram for master receiver when N=2

1. The EV5, EV6 and EV9 events stretch SCL low until the end of the corresponding software sequence.

2. The EV6_1 software sequence must complete before the ACK pulse of the current byte transfer.

AAddressS

EV5 EV6

AData1 Data2

EV7_3

NA P

Legend: S = Start, S

r

= Repeated Start, P = Stop, A = Acknowledge, NA = Non-acknowledge,

EV5: SB=1, cleared by reading SR1 register followed by writing the DR register.

EV6: ADDR1, cleared by reading SR1 register followed by reading SR2.

In 10-bit master receiver mode, this sequence should be followed by writing CR2 with START = 1.

EV6_1: No associated flag event. The acknowledge disable should be done just after EV6, that is after ADDR is cleared.

EVx = Event (with interrupt if ITEVFEN = 1)

EV6_1

EV7_3: BTF = 1, program STOP = 1, read DR twice (Read Data1 and Data2) just after programming the STOP.

7- bit master receiver

10- bit master receiver

AHeaderS

EV5 EV9

AAddress

EV6

AData1 Data2

EV7_3

NA P

EV6_1

AHeaderS

r

EV5

EV6

EV9: ADD10= 1, cleared by reading SR1 register followed by writing DR register.

Loading...

Loading...