RM0008 Ethernet (ETH): media access control (MAC) with DMA controller

Doc ID 13902 Rev 12 987/1096

indicates the last buffer of the frame. After the last buffer of the frame has been transmitted,

the DMA writes back the final status information to the transmit descriptor 0 (TDES0) word

of the descriptor that has the last segment set in transmit descriptor 0 (TDES0[29]). At this

time, if Interrupt on Completion (TDES0[30]) is set, Transmit Interrupt (in ETH_DMASR

register [0]) is set, the next descriptor is fetched, and the process repeats. Actual frame

transmission begins after the Transmit FIFO has reached either a programmable transmit

threshold (ETH_DMAOMR register[16:14]), or a full frame is contained in the FIFO. There is

also an option for the Store and forward mode (ETH_DMAOMR register[21]). Descriptors

are released (OWN bit TDES0[31] is cleared) when the DMA finishes transferring the frame.

Transmit polling suspended

Transmit polling can be suspended by either of the following conditions:

● The DMA detects a descriptor owned by the CPU (TDES0[31]=0) and the Transmit

buffer unavailable flag is set (ETH_DMASR register[2]). To resume, the driver must give

descriptor ownership to the DMA and then issue a Poll Demand command.

● A frame transmission is aborted when a transmit error due to underflow is detected.

The appropriate Transmit Descriptor 0 (TDES0) bit is set. If the second condition

occurs, both the Abnormal Interrupt Summary (in ETH_DMASR register [15]) and

Transmit Underflow bits (in ETH_DMASR register[5]) are set, and the information is

written to Transmit Descriptor 0, causing the suspension. If the DMA goes into Suspend

state due to the first condition, then both the Normal Interrupt Summary (ETH_DMASR

register [16]) and Transmit Buffer Unavailable (ETH_DMASR register[2]) bits are set. In

both cases, the position in the transmit list is retained. The retained position is that of

the descriptor following the last descriptor closed by the DMA. The driver must explicitly

issue a Transmit Poll Demand command after rectifying the suspension cause.

Tx DMA descriptors

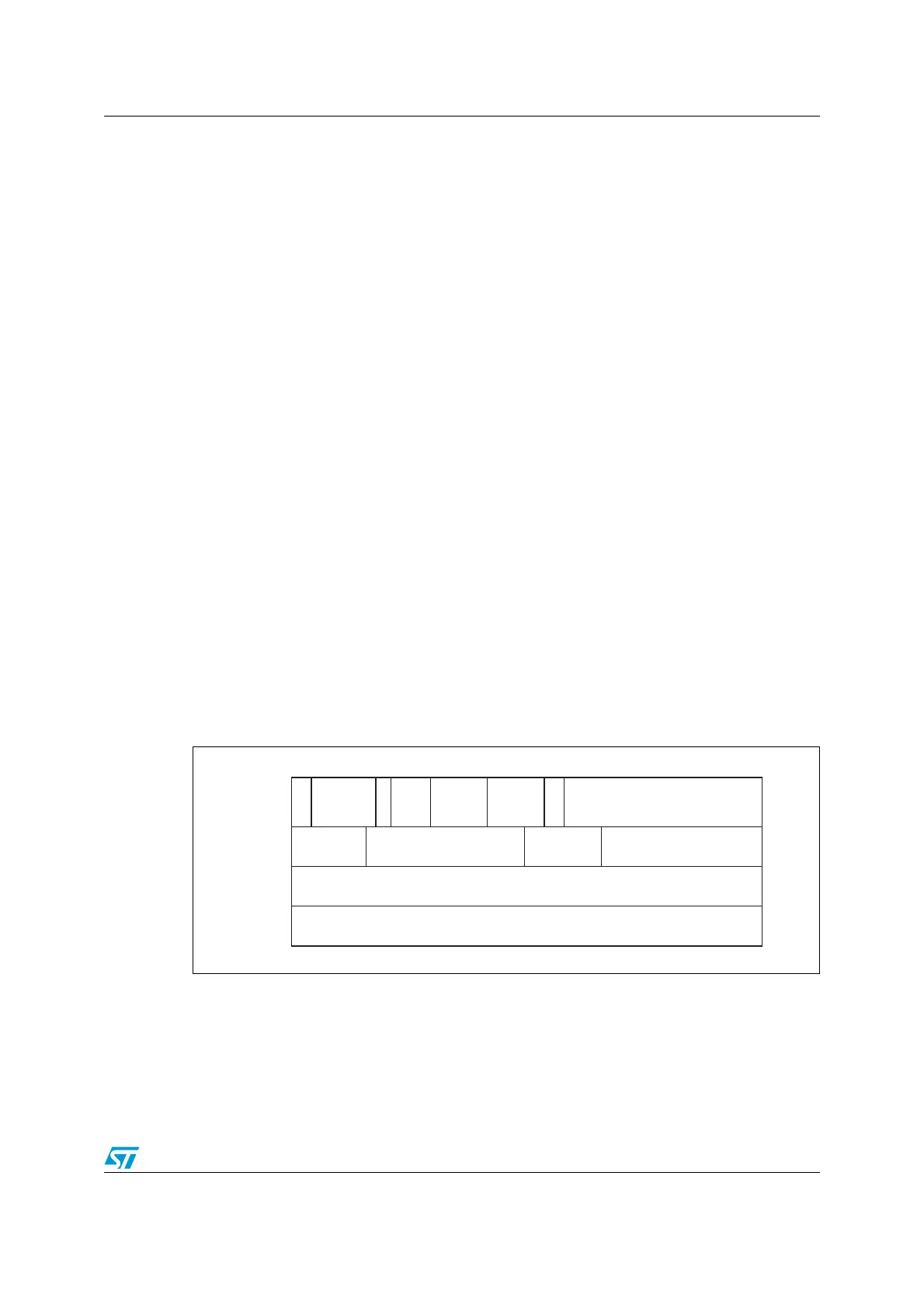

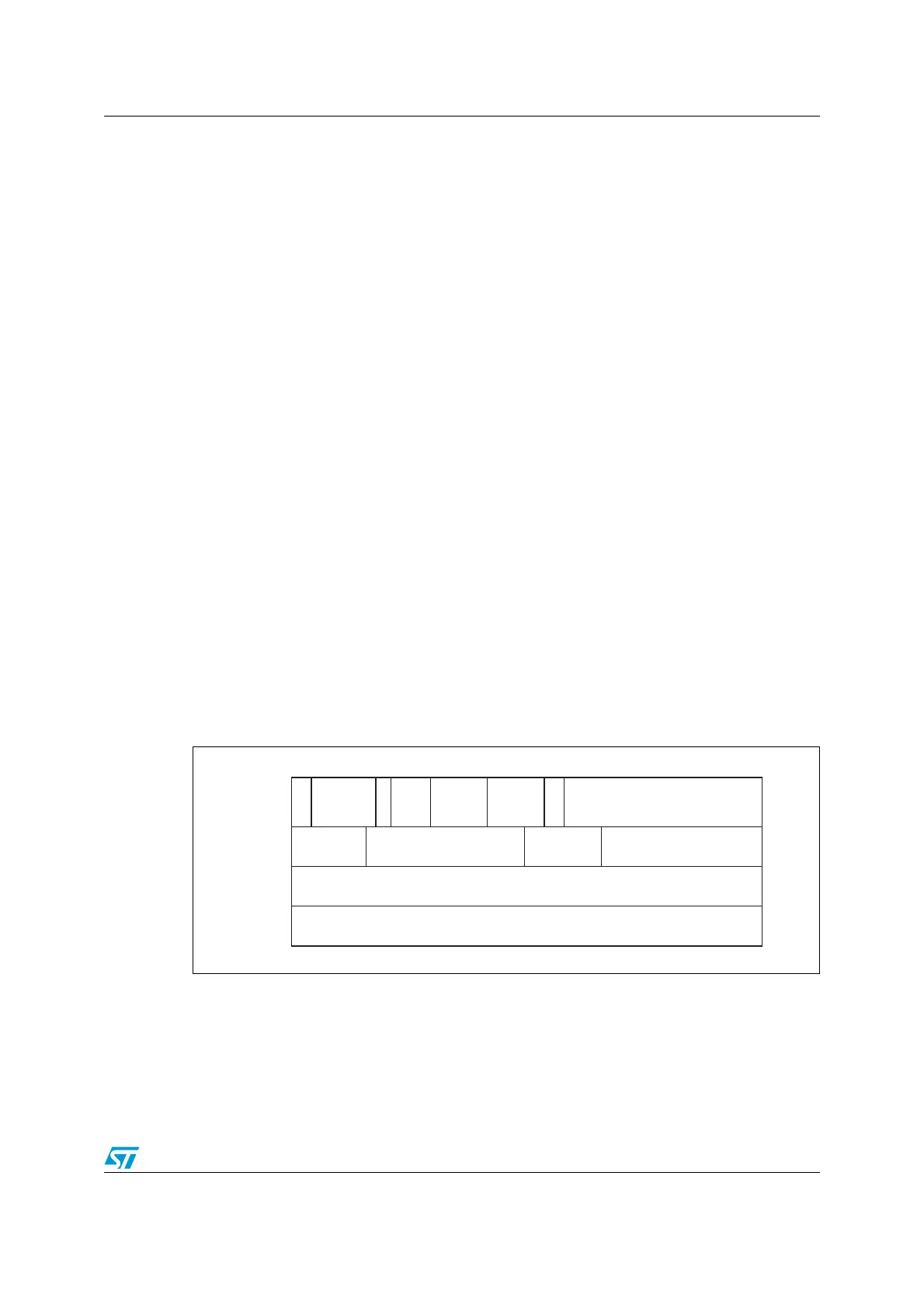

The descriptor structure consists of four 32-bit words as shown in Figure 354. The bit

descriptions of TDES0, TDES1, TDES2 and TDES3 are given below.

Figure 354. Transmit descriptor

TDES 3

O

W

N

Ctrl

[30:26]

Res.

24

Ctrl

[23:20]

Reserved

[19:18]

Status [16:0]

Reserved

[31:29]

Buffer 2 byte count

[28:16]

Reserved

[15:13]

Buffer 1 byte count

[12:0]

Buffer 1 address [31:0] / Time stamp low [31:0]

Buffer 2 address [31:0] or Next descriptor address [31:0] / Time stamp high [31:0]

TDES 0

TDES 1

TDES 2

31 0

ai15642b

T

T

S

E

T

T

S

S

Loading...

Loading...