Low-, medium-, high- and XL-density reset and clock control (RCC) RM0008

108/1096 Doc ID 13902 Rev 12

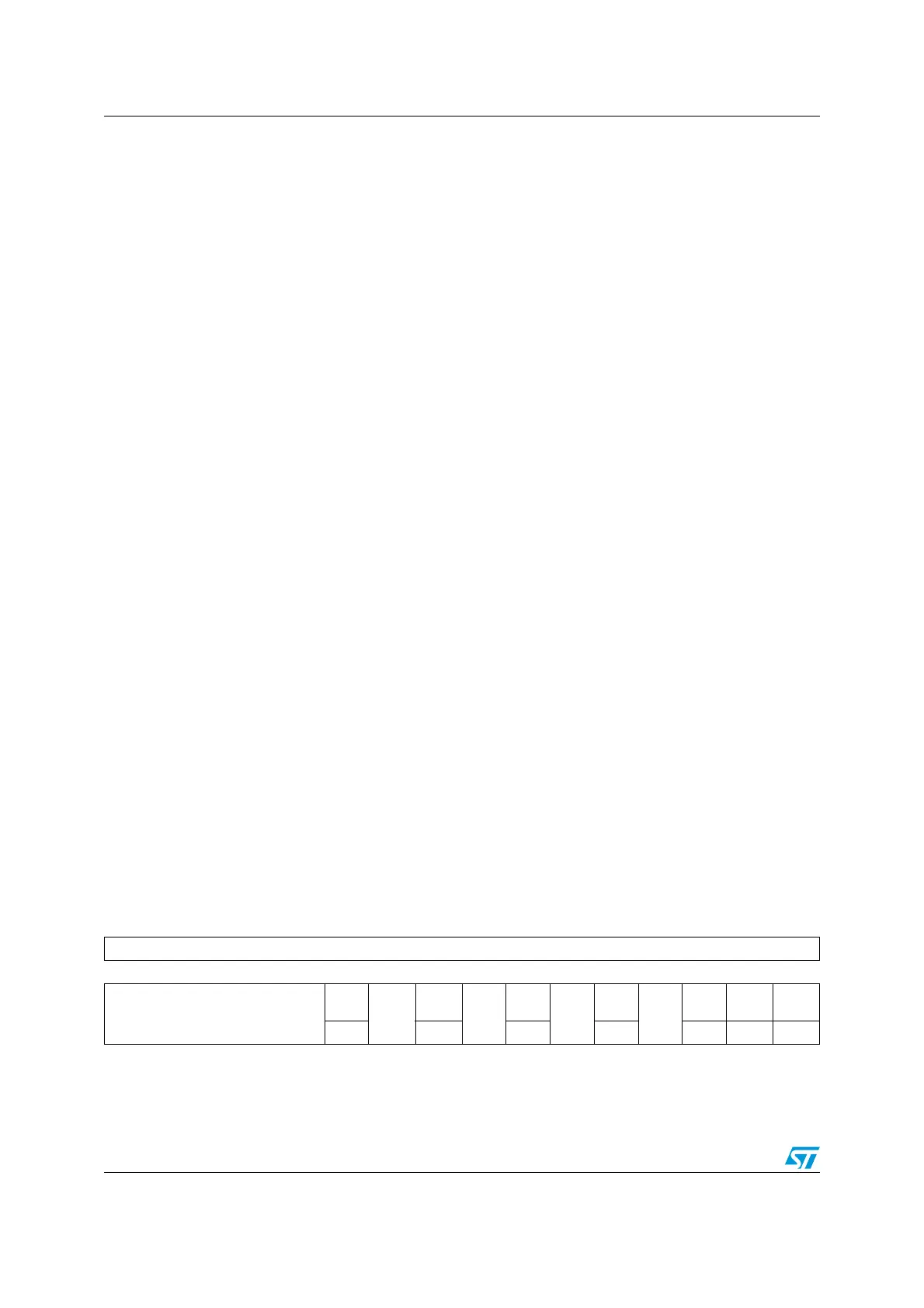

7.3.6 AHB peripheral clock enable register (RCC_AHBENR)

Address offset: 0x14

Reset value: 0x0000 0014

Access: no wait state, word, half-word and byte access

Note: When the peripheral clock is not active, the peripheral register values may not be readable

by software and the returned value is always 0x0.

Bit 6 TIM12RST: TIM12 timer reset

Set and cleared by software.

0: No effect

1: Reset TIM12

Bit 5 TIM7RST: TIM7 timer reset

Set and cleared by software.

0: No effect

1: Reset TIM7

Bit 4 TIM6RST: TIM6 timer reset

Set and cleared by software.

0: No effect

1: Reset TIM6

Bit 3 TIM5RST: TIM5 timer reset

Set and cleared by software.

0: No effect

1: Reset TIM5

Bit 2 TIM4RST: TIM4 timer reset

Set and cleared by software.

0: No effect

1: Reset TIM4

Bit 1 TIM3RST: TIM3 timer reset

Set and cleared by software.

0: No effect

1: Reset TIM3

Bit 0 TIM2RST: TIM2 timer reset

Set and cleared by software.

0: No effect

1: Reset TIM2

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

SDIO

EN

Res.

FSMC

EN

Res.

CRCE

N

Res.

FLITF

EN

Res.

SRAM

EN

DMA2

EN

DMA1

EN

rw rw rw rw rw rw rw

Bits 31:11 Reserved, always read as 0.

Loading...

Loading...