RM0008 Flexible static memory controller (FSMC)

Doc ID 13902 Rev 12 505/1096

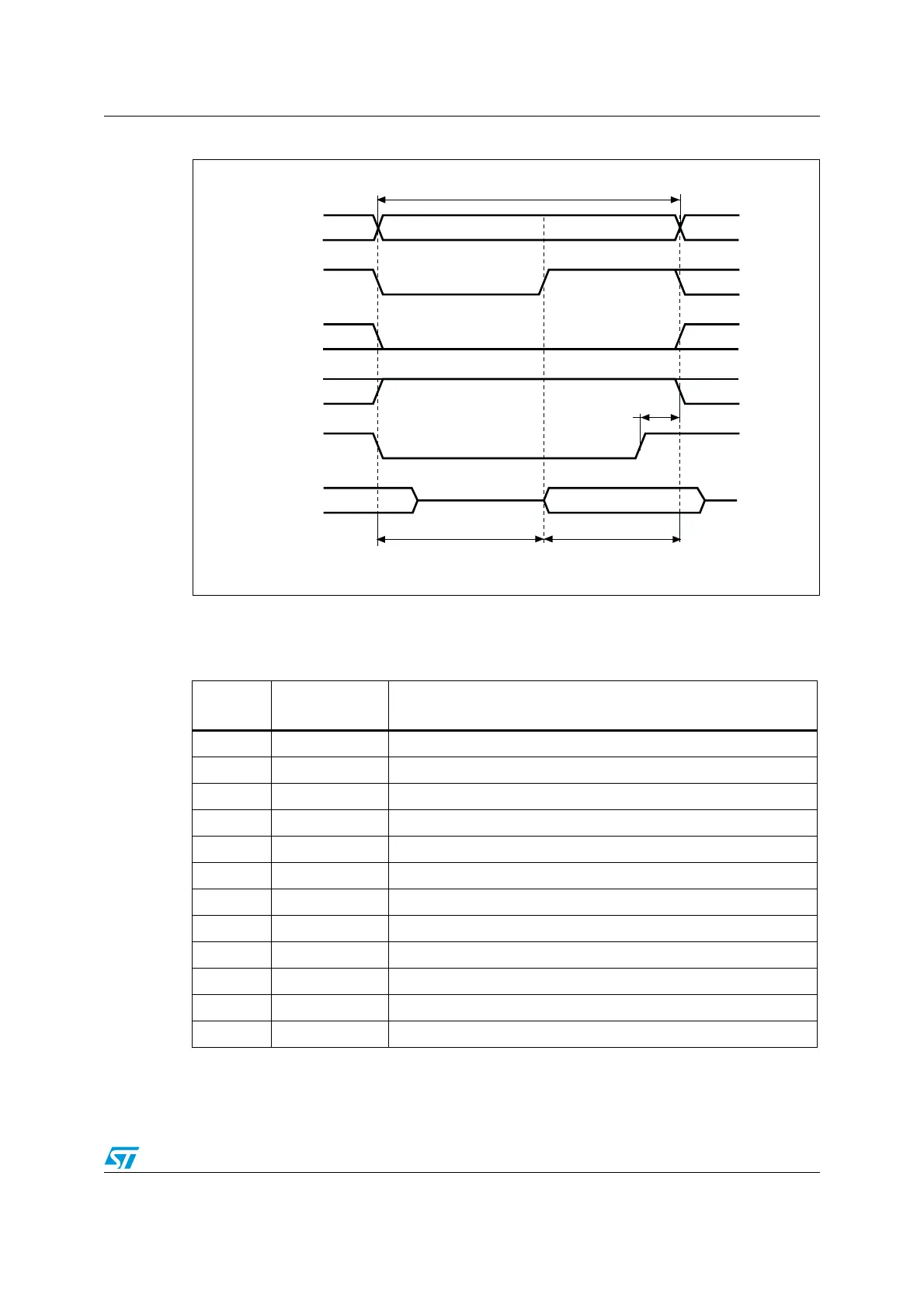

Figure 193. ModeB write accesses

The differences with mode1 are the toggling of NADV and the independent read and write

timings when extended mode is set (Mode B).

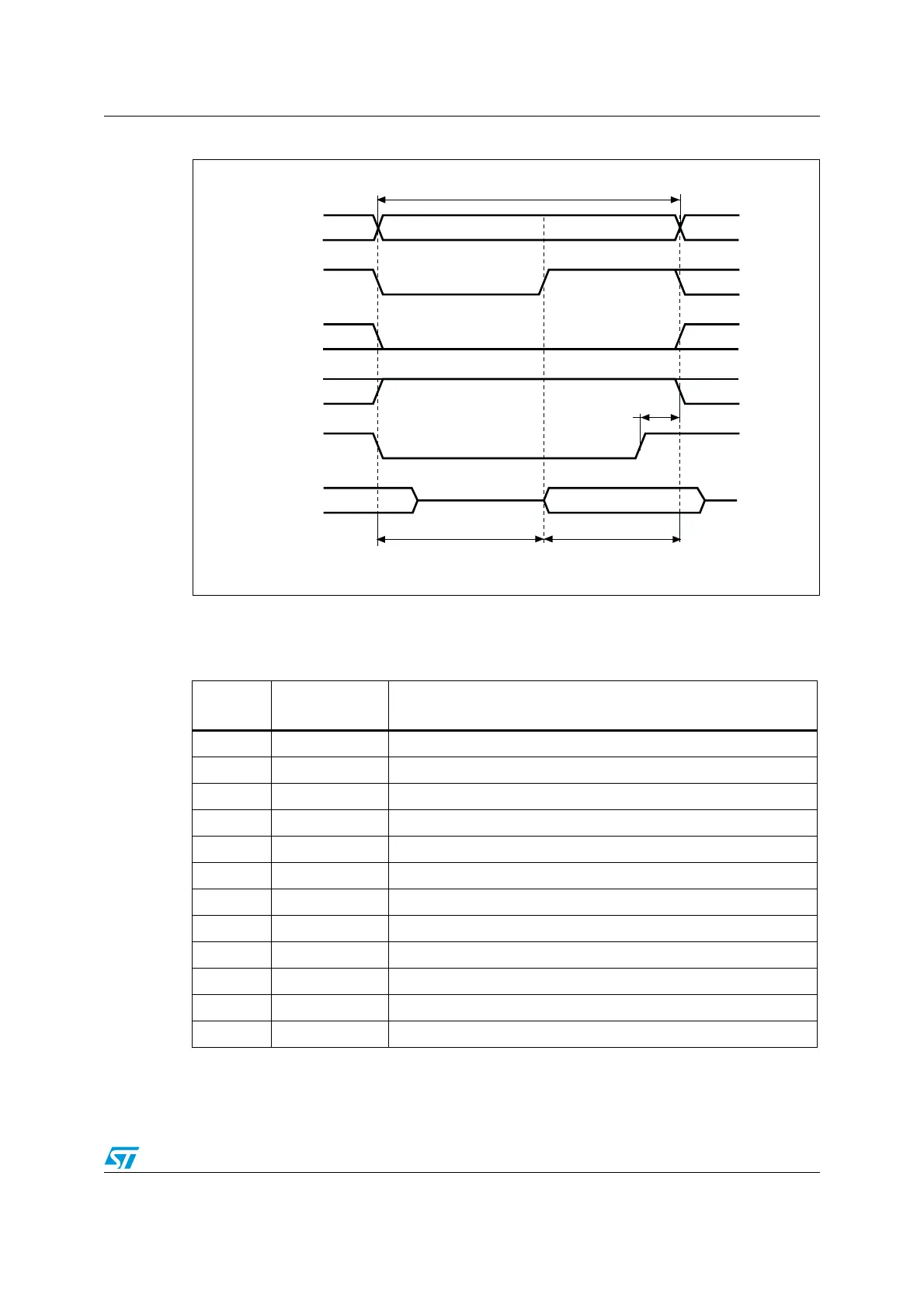

Table 113. FSMC_BCRx bit fields

Bit

number

Bit name Value to set

31-16 0x0000

15 ASYNCWAIT Set to 1 if the memory supports this feature. Otherwise keep at 0.

14 EXTMOD 0x1 for mode B, 0x0 for mode 2

13-10 0x0

9 WAITPOL Meaningful only if bit 15 is 1

8 BURSTEN 0x0

7 -

6 FACCEN 0x1

5-4 MWID As needed

3-2 MTYP 10 (NOR Flash)

1 MUXEN 0x0

0 MBKEN 0x1

A[25:0]

NOE

(ADDSET +1) (DATAST + 1)

Memory transaction

NEx

D[15:0]

HCLK cycles HCLK cycles

NWE

NADV

data driven by FSMC

ai15110b

1HCLK

Loading...

Loading...