Advanced-control timers (TIM1&TIM8) RM0008

292/1096 Doc ID 13902 Rev 12

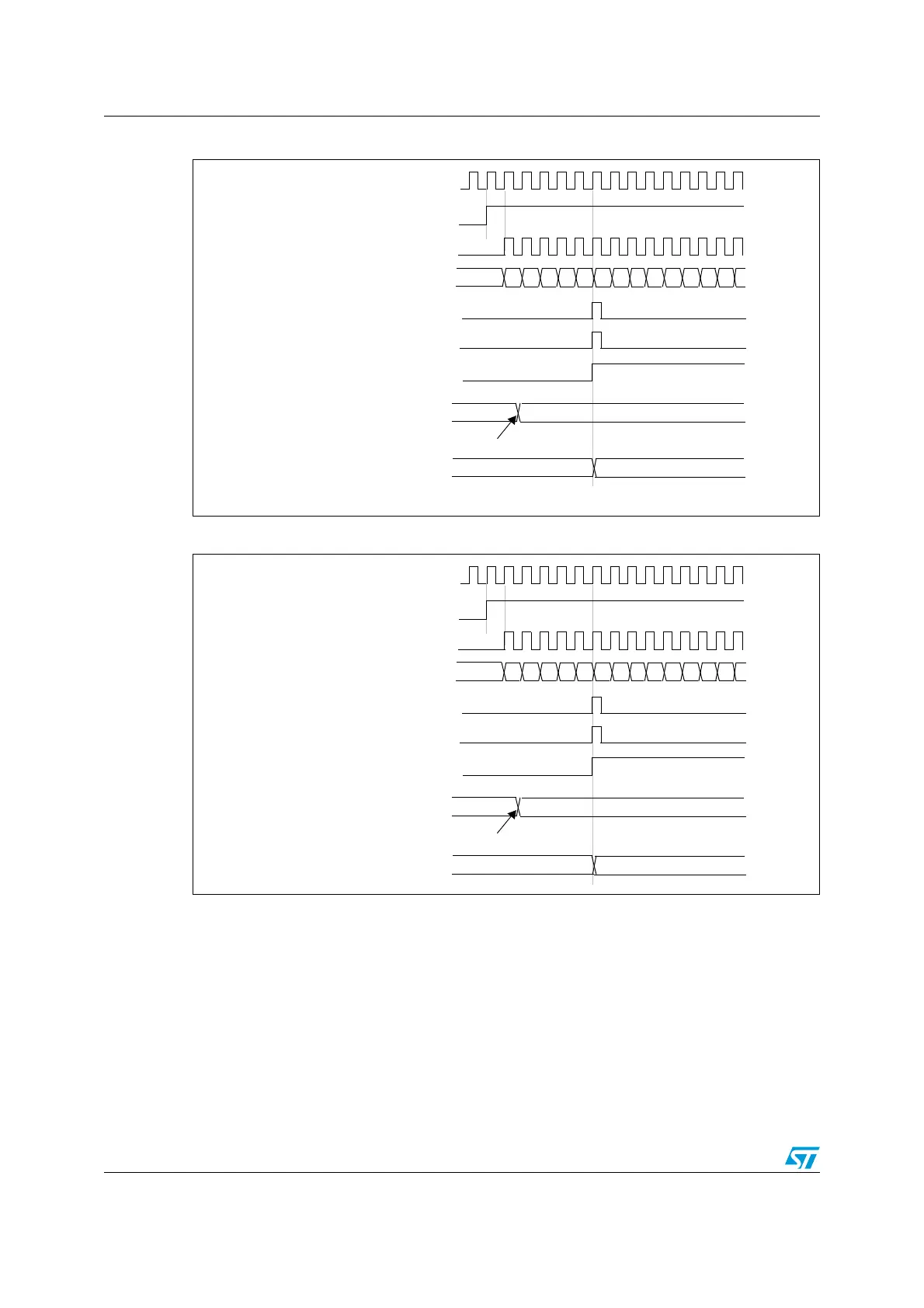

Figure 70. Counter timing diagram, update event with ARPE=1 (counter underflow)

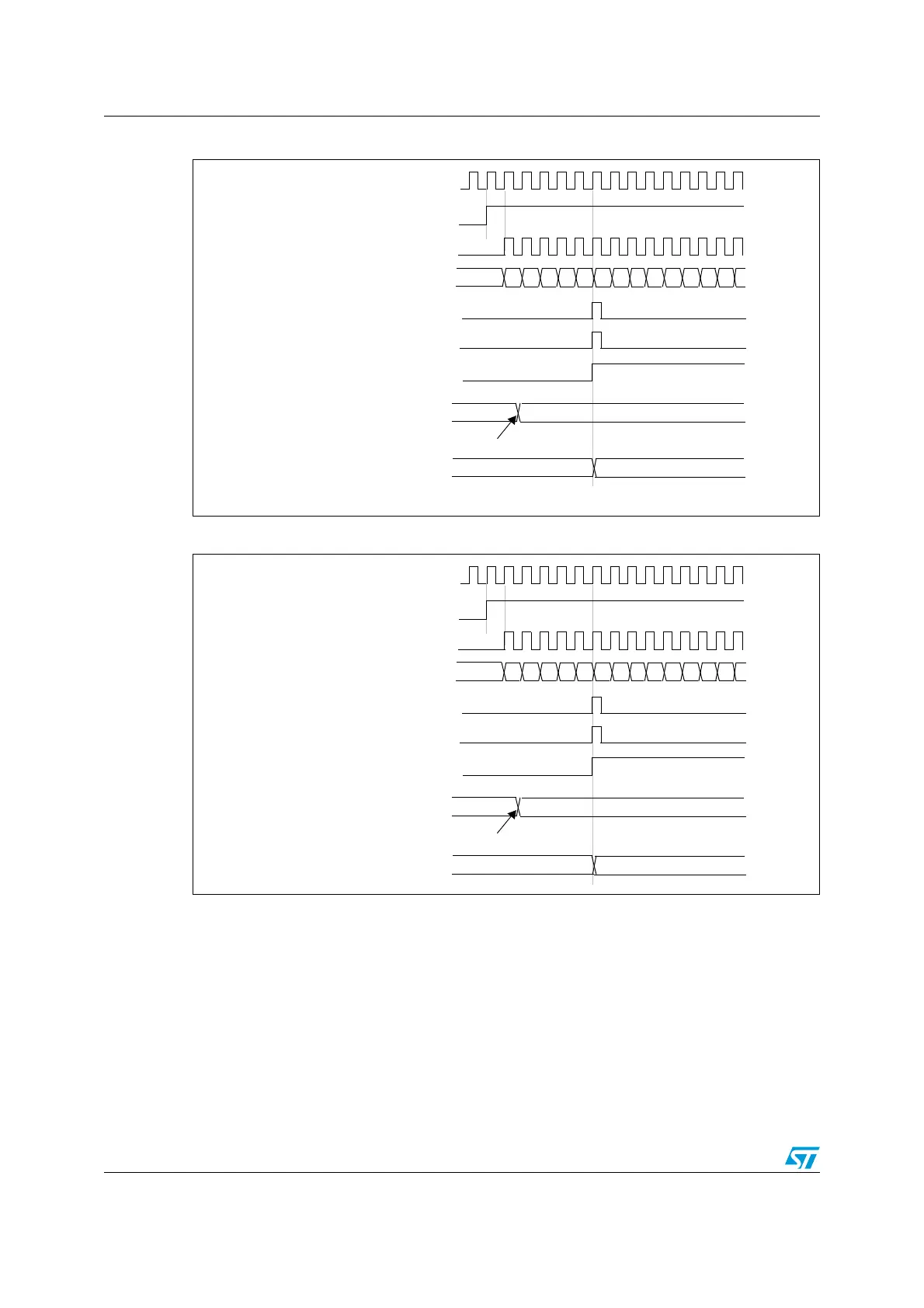

Figure 71. Counter timing diagram, Update event with ARPE=1 (counter overflow)

14.3.3 Repetition counter

Section 14.3.1: Time-base unit describes how the update event (UEV) is generated with

respect to the counter overflows/underflows. It is actually generated only when the repetition

counter has reached zero. This can be useful when generating PWM signals.

This means that data are transferred from the preload registers to the shadow registers

(TIMx_ARR auto-reload register, TIMx_PSC prescaler register, but also TIMx_CCRx

capture/compare registers in compare mode) every N counter overflows or underflows,

where N is the value in the TIMx_RCR repetition counter register.

CK_PSC

00

CEN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

Counter underflow

Update event (UEV)

01 02 03 04 05 06 0705 04 03 02 0106

Auto-reload preload register

FD 36

Write a new value in TIMx_ARR

Auto-reload active register

FD 36

CK_PSC

36

CEN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

Counter overflow

Update event (UEV)

35 34 33 32 31 30 2FF8 F9 FA FB FCF7

Auto-reload preload register

FD 36

Write a new value in TIMx_ARR

Auto-reload active register

FD 36

Loading...

Loading...