Digital-to-analog converter (DAC) RM0008

262/1096 Doc ID 13902 Rev 12

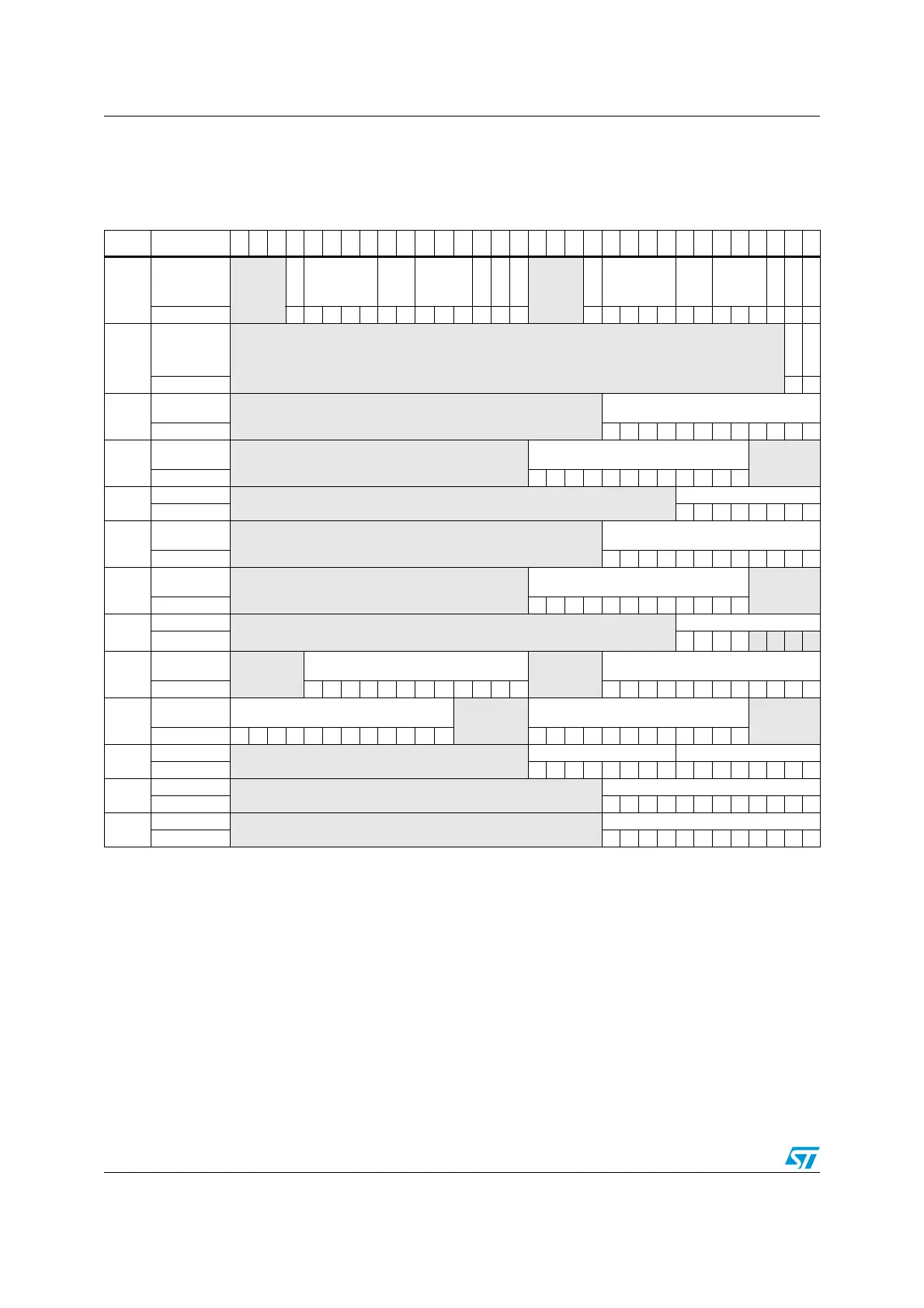

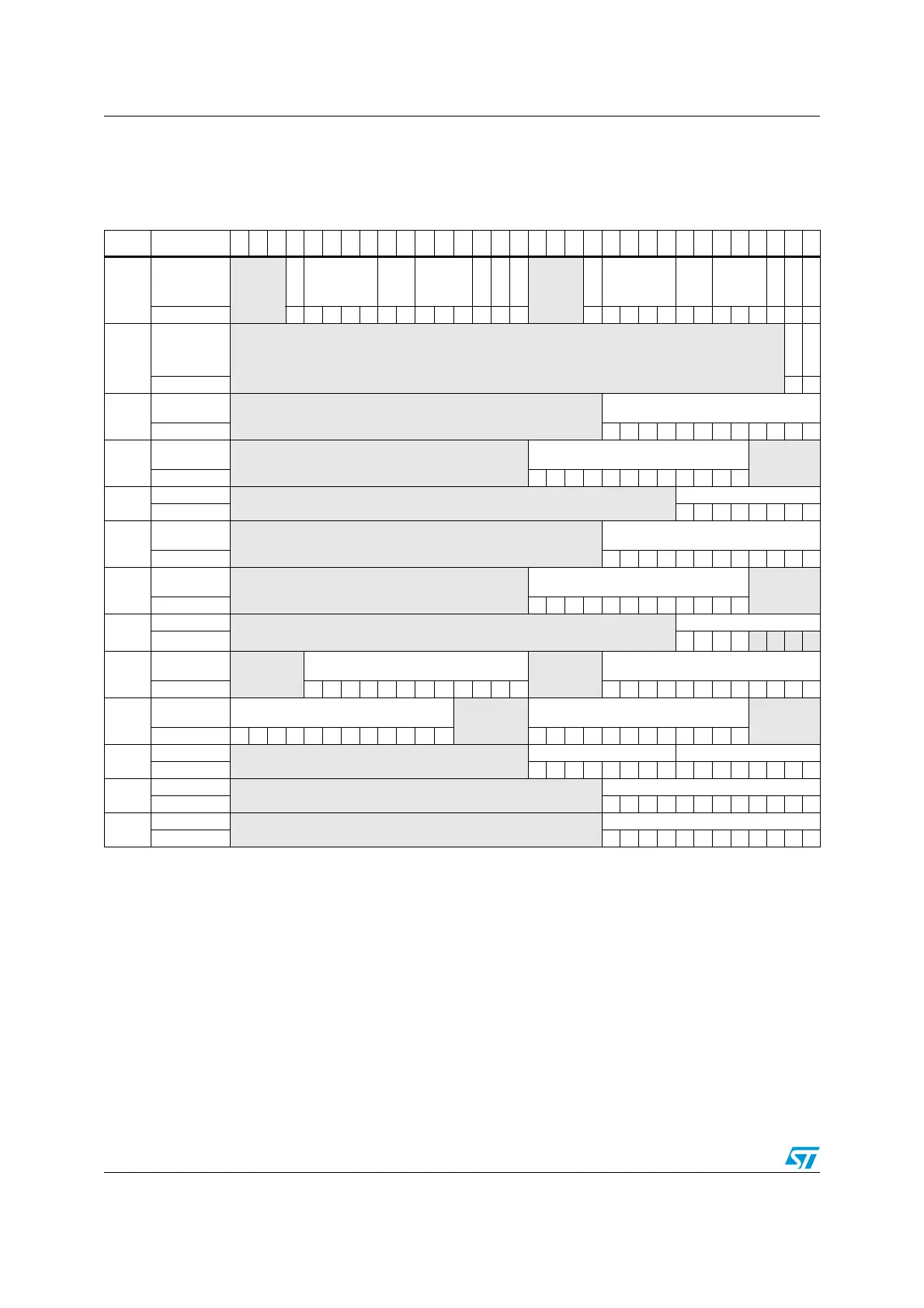

12.5.14 DAC register map

The following table summarizes the DAC registers.

Note: Refer to Table 3 on page 50 for the register boundary addresses.

Table 75. DAC register map

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00

DAC_CR

Reserved

DMAEN2

MAMP2[3:0]

WAVE

2[2:0]

TSEL2[2:0]

TEN2

BOFF2

EN2

Reserved

DMAEN1

MAMP1[3:0]

WAVE

1[2:0]

TSEL1

[2:0]

TEN1

BOFF1

EN1

Reset value 0000000000000 0000000000000

0x04

DAC_SWTRIG

R

Reserved

SWTRIG2

SWTRIG1

Reset value 00

0x08

DAC_DHR12R

1

Reserved

DACC1DHR[11:0]

Reset value 000000000000

0x0C

DAC_DHR12L

1

Reserved

DACC1DHR[11:0]

Reserved

Reset value 000000000000

0x10

DAC_DHR8R1

Reserved

DACC1DHR[7:0]

Reset value 00000000

0x14

DAC_DHR12R

2

Reserved

DACC2DHR[11:0]

Reset value 000000000000

0x18

DAC_DHR12L

2

Reserved

DACC2DHR[11:0]

Reserved

Reset value 000000000000

0x1C

DAC_DHR8R2

Reserved

DACC2DHR[7:0]

0x20

DAC_DHR12R

D

Reserved

DACC2DHR[11:0]

Reserved

DACC1DHR[11:0]

Reset value 000000000000 000000000000

0x24

DAC_DHR12L

D

DACC2DHR[11:0]

Reserved

DACC1DHR[11:0]

Reserved

Reset value 000000000000 000000000000

0x28

DAC_DHR8RD

Reserved

DACC2DHR[7:0] DACC1DHR[7:0]

Reset value 0000000000000000

0x2C

DAC_DOR1

Reserved

DACC1DOR[11:0]

Reset value 000000000000

0x30

DAC_DOR2

Reserved

DACC2DOR[11:0]

Reset value 000000000000

Loading...

Loading...