Real-time clock (RTC) RM0008

472/1096 Doc ID 13902 Rev 12

RTC prescaler load register low (RTC_PRLL)

Address offset: 0x0C

Write only (see Section 18.3.4 on page 467)

Reset value: 0x8000

Note: If the input clock frequency (f

RTCCLK

) is 32.768 kHz, write 7FFFh in this register to get a

signal period of 1 second.

18.4.4 RTC prescaler divider register (RTC_DIVH / RTC_DIVL)

During each period of TR_CLK, the counter inside the RTC prescaler is reloaded with the

value stored in the RTC_PRL register. To get an accurate time measurement it is possible to

read the current value of the prescaler counter, stored in the RTC_DIV register, without

stopping it. This register is read-only and it is reloaded by hardware after any change in the

RTC_PRL or RTC_CNT registers.

RTC prescaler divider register high (RTC_DIVH)

Address offset: 0x10

Reset value: 0x0000

RTC prescaler divider register low (RTC_DIVL)

Address offset: 0x14

Reset value: 0x8000

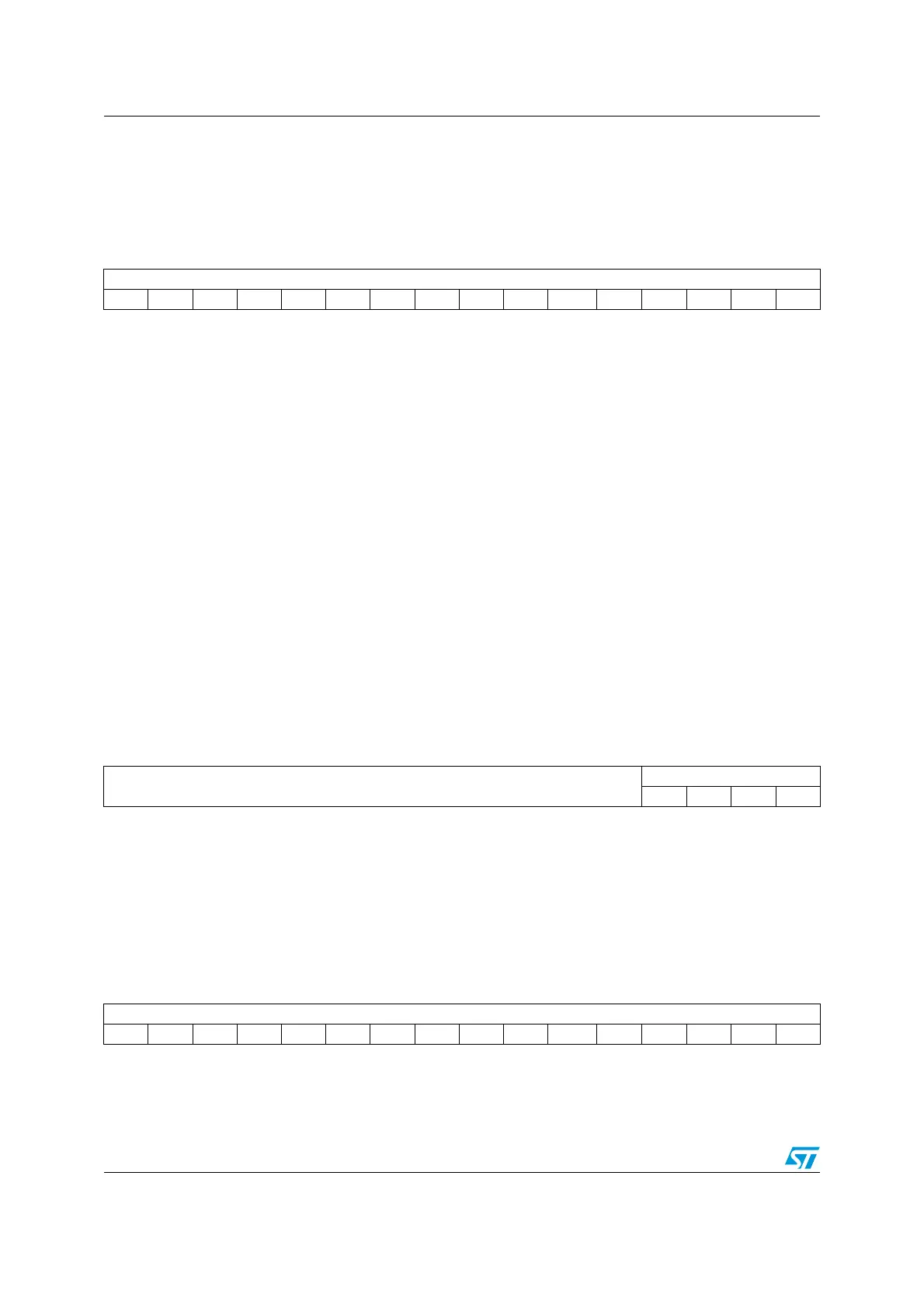

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PRL[15:0]

wwwwwwwwww w wwwww

Bits 15:0 PRL[15:0]: RTC prescaler reload value low

These bits are used to define the counter clock frequency according to the following formula:

f

TR_CLK

= f

RTCCLK

/(PRL[19:0]+1)

Caution: The zero value is not recommended. RTC interrupts and flags cannot be

asserted correctly.

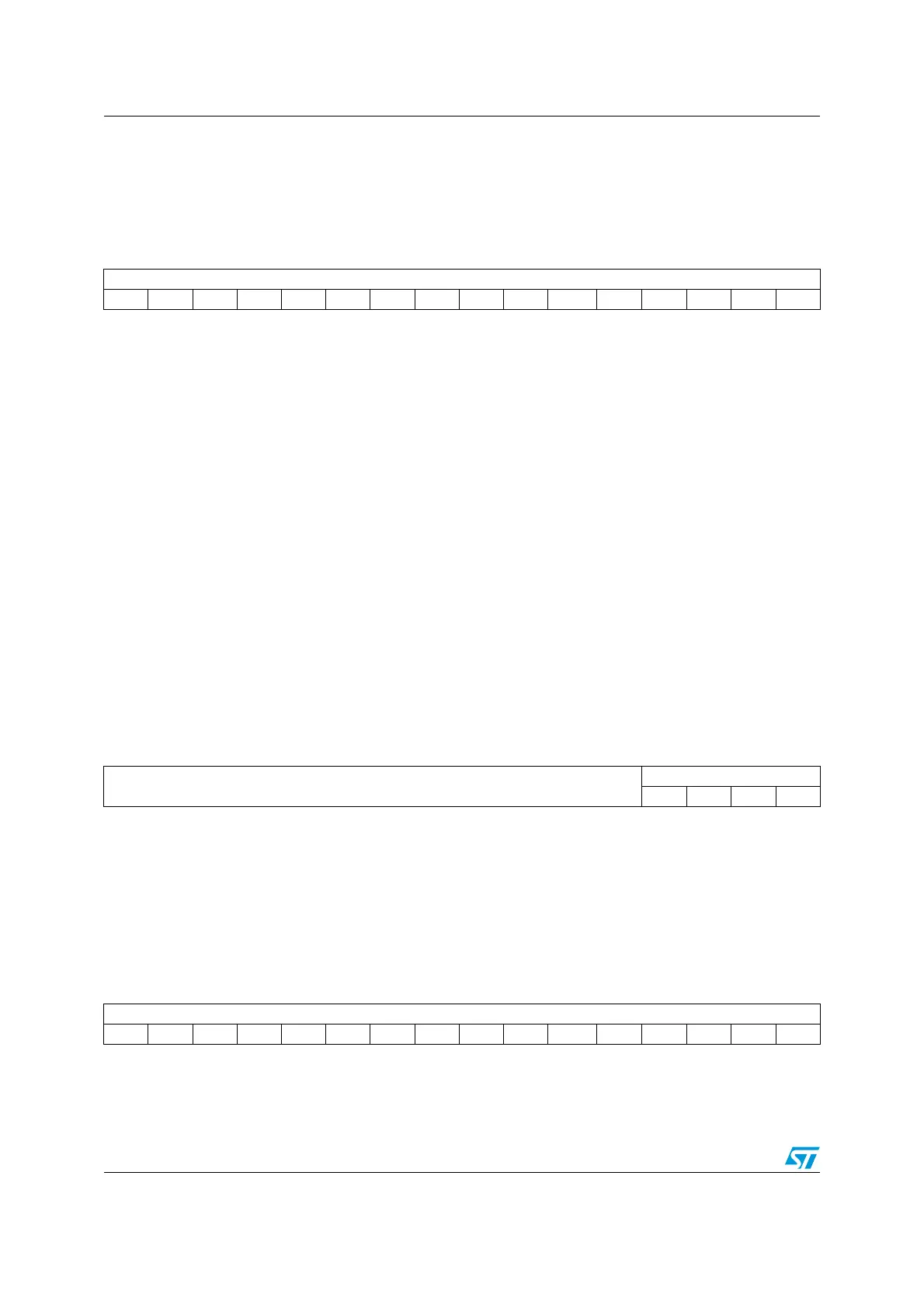

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

RTC_DIV[19:16]

rrrr

Bits 15:4 Reserved

Bits 3:0 RTC_DIV[19:16]: RTC clock divider high

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RTC_DIV[15:0]

rrrrrrrrrr r rrrrr

Bits 15:0 RTC_DIV[15:0]: RTC clock divider low

Loading...

Loading...