General-purpose timers (TIM9 to TIM14) RM0008

432/1096 Doc ID 13902 Rev 12

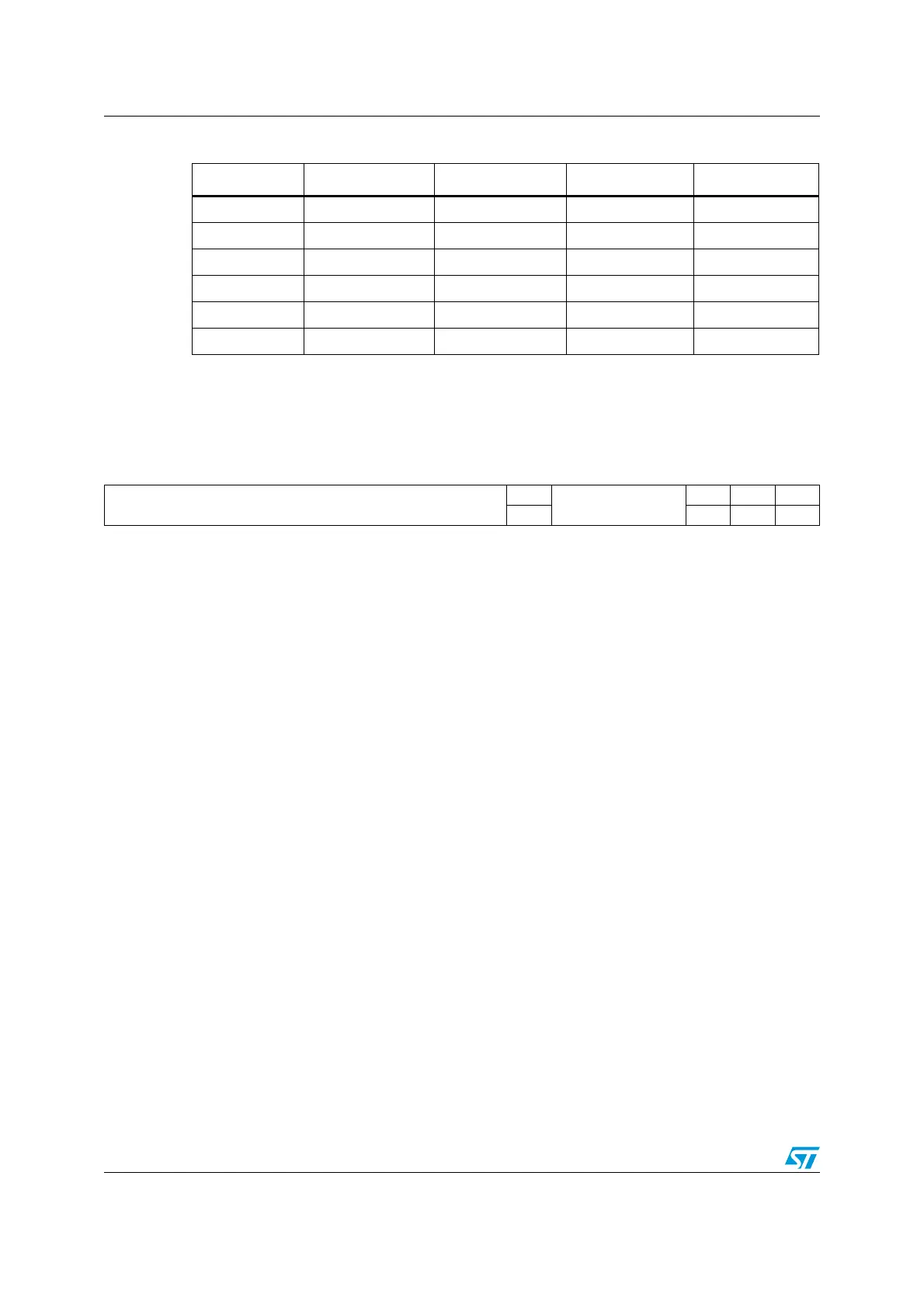

16.5.4 TIM9/12 Interrupt enable register (TIMx_DIER)

Address offset: 0x0C

Reset value: 0x0000

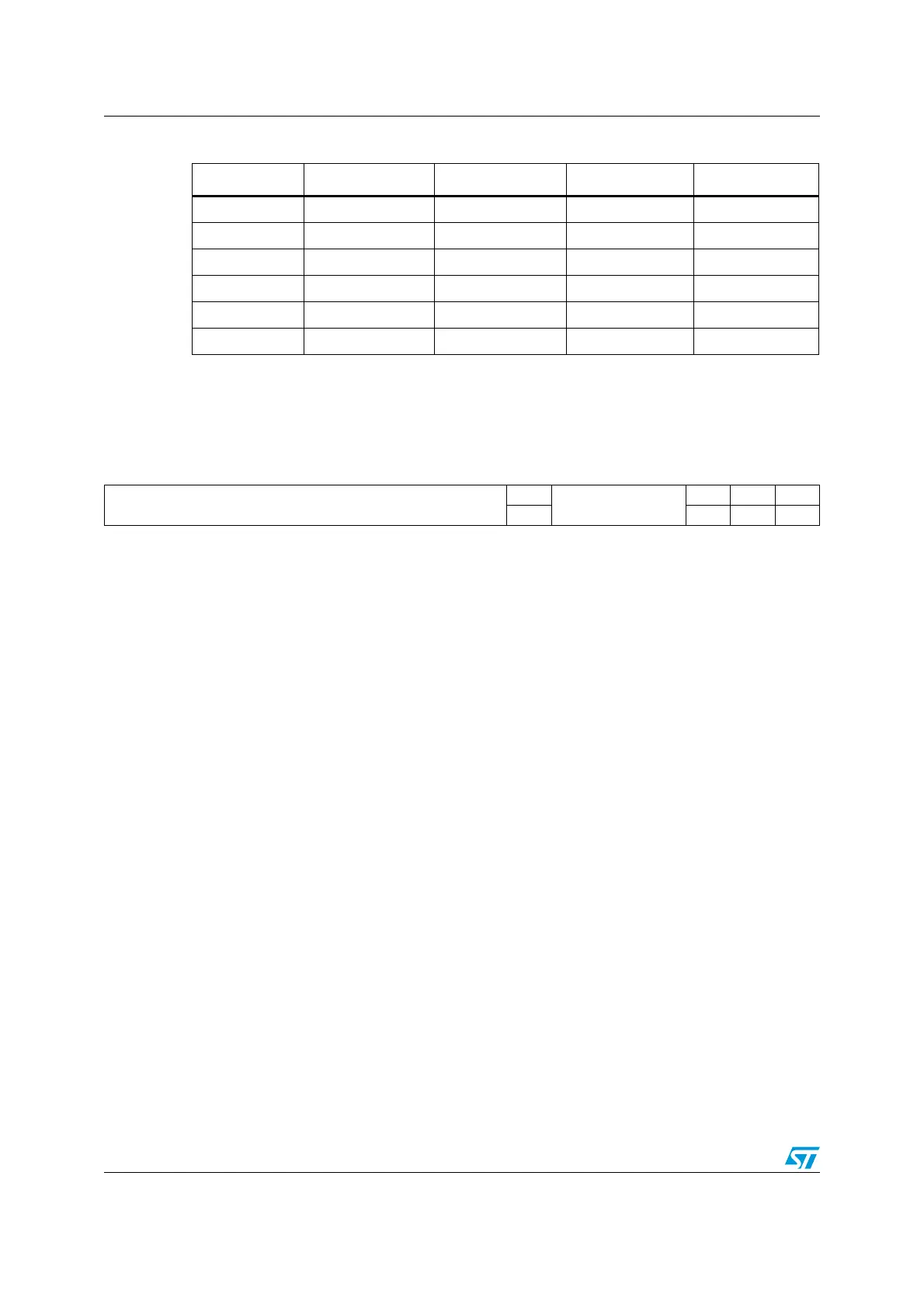

Table 89. TIMx internal trigger connection

Slave TIM ITR0 (TS =’ 000’) ITR1 (TS = ‘001’) ITR2 (TS = ‘010’) ITR3 (TS = ’011’)

TIM2 TIM1 TIM8 TIM3 TIM4

TIM3 TIM1 TIM2 TIM5 TIM4

TIM4 TIM1 TIM2 TIM3 TIM8

TIM5 TIM2 TIM3 TIM4 TIM8

TIM9 TIM2 TIM3 TIM10 TIM11

TIM12 TIM4 TIM5 TIM13 TIM14

1514131211109876543210

Reserved

TIE

Res

CC2IE CC1IE UIE

rw rw rw rw

Bit 15:7 Reserved, always read as 0.

Bit 6 TIE: Trigger interrupt enable

0: Trigger interrupt disabled.

1: Trigger interrupt enabled.

Bit 5:3 Reserved, always read as 0.

Bit 2 CC2IE: Capture/Compare 2 interrupt enable

0: CC2 interrupt disabled.

1: CC2 interrupt enabled.

Bit 1 CC1IE: Capture/Compare 1 interrupt enable

0: CC1 interrupt disabled.

1: CC1 interrupt enabled.

Bit 0 UIE: Update interrupt enable

0: Update interrupt disabled.

1: Update interrupt enabled.

Loading...

Loading...