USB on-the-go full-speed (OTG_FS) RM0008

840/1096 Doc ID 13902 Rev 12

OTG_FS core interrupt register (OTG_FS_GINTSTS)

Address offset: 0x014

Reset value: 0x0400 0020

This register interrupts the application for system-level events in the current mode (device

mode or host mode).

Some of the bits in this register are valid only in host mode, while others are valid in device

mode only. This register also indicates the current mode. To clear the interrupt status bits of

the rc_w1 type, the application must write 1 into the bit.

The FIFO status interrupts are read-only; once software reads from or writes to the FIFO

while servicing these interrupts, FIFO interrupt conditions are cleared automatically.

The application must clear the OTG_FS_GINTSTS register at initialization before

unmasking the interrupt bit to avoid any interrupts generated prior to initialization.

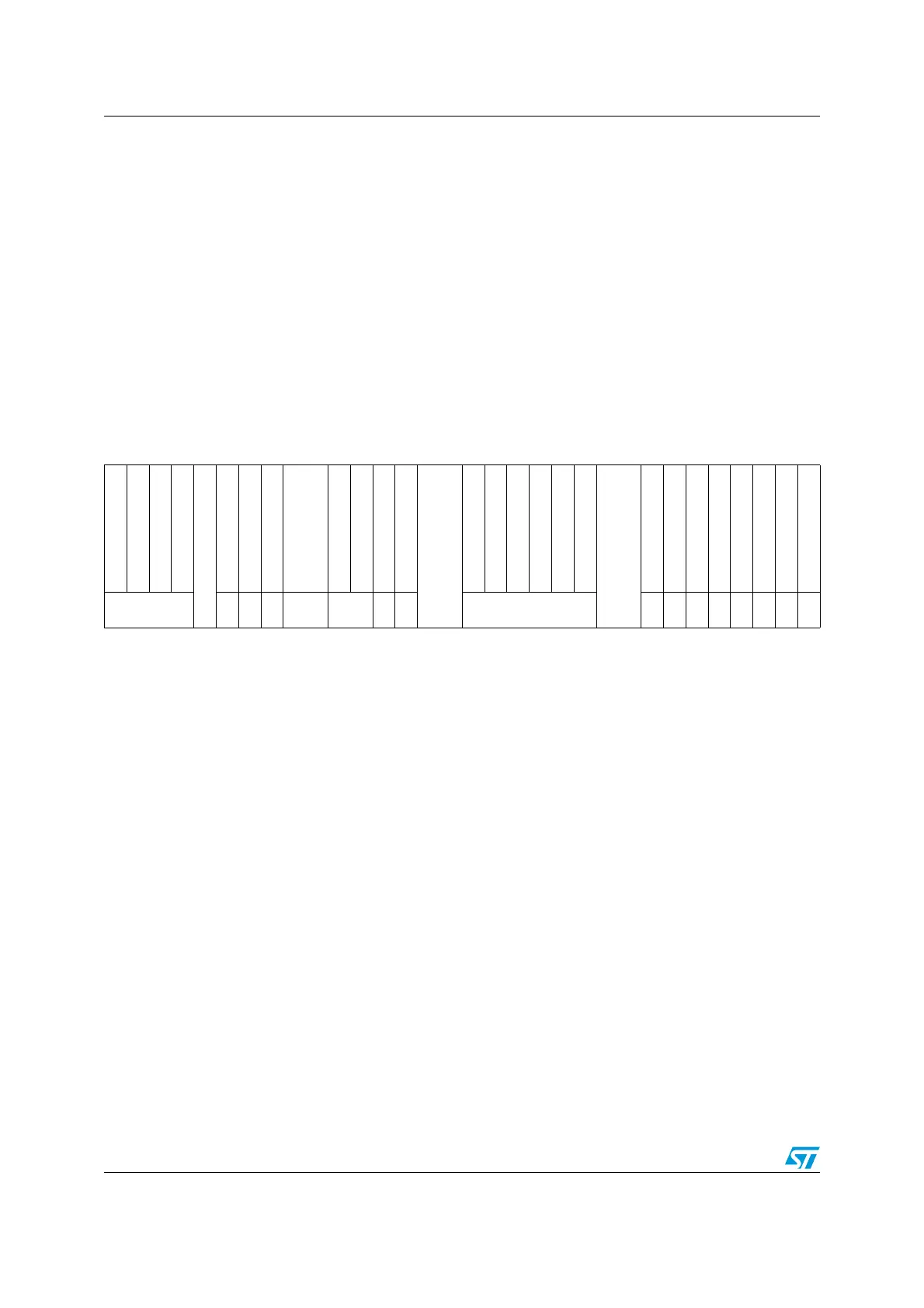

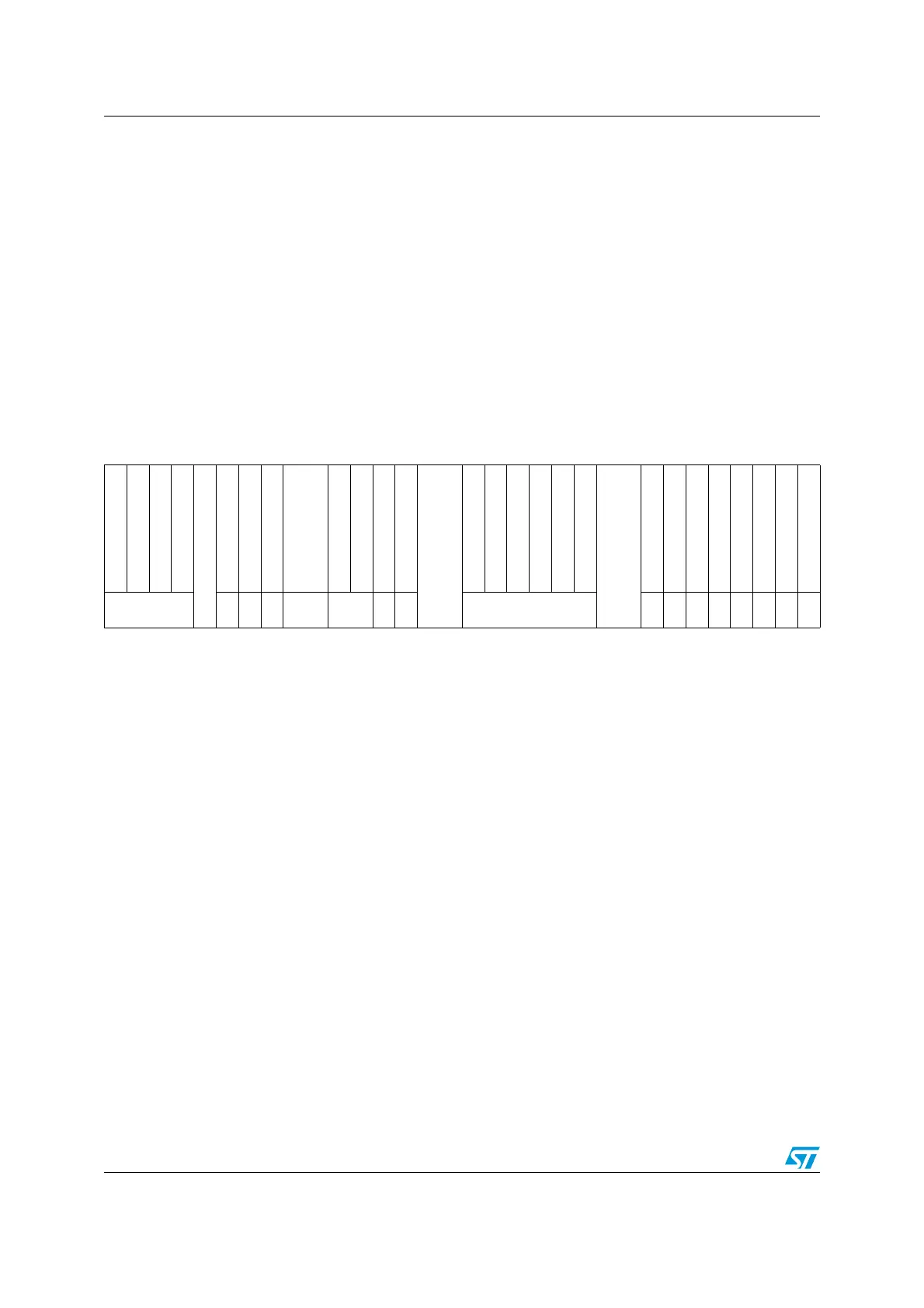

313029282726252423222120191817161514131211109876543210

WKUINT

SRQINT

DISCINT

CIDSCHG

Reserved

PTXFE

HCINT

HPRTINT

Reserved

IPXFR/INCOMPISOOUT

IISOIXFR

OEPINT

IEPINT

Reserved

EOPF

ISOODRP

ENUMDNE

USBRST

USBSUSP

ESUSP

Reserved

GOUTNAKEFF

GINAKEFF

NPTXFE

RXFLVL

SOF

OTGINT

MMIS

CMOD

rc_w1 rrr Res.rc_w1rr rc_w1 rrrr

rc_w1

r

rc_w1

r

Bit 31 WKUPINT: Resume/remote wakeup detected interrupt

In device mode, this interrupt is asserted when a resume is detected on the USB. In host

mode, this interrupt is asserted when a remote wakeup is detected on the USB.

Note: Accessible in both device and host modes.

Bit 30 SRQINT: Session request/new session detected interrupt

In host mode, this interrupt is asserted when a session request is detected from the device. In

device mode, this interrupt is asserted when V

BUS

is in the valid range for a B-peripheral

device. Accessible in both device and host modes.

Bit 29 DISCINT: Disconnect detected interrupt

Asserted when a device disconnect is detected.

Note: Only accessible in host mode.

Bit 28 CIDSCHG: Connector ID status change

The core sets this bit when there is a change in connector ID status.

Note: Accessible in both device and host modes.

Bit 27 Reserved

Bit 26 PTXFE: Periodic TxFIFO empty

Asserted when the periodic transmit FIFO is either half or completely empty and there is space

for at least one entry to be written in the periodic request queue. The half or completely empty

status is determined by the periodic TxFIFO empty level bit in the OTG_FS_GAHBCFG

register (PTXFELVL bit in OTG_FS_GAHBCFG).

Note: Only accessible in host mode.

Loading...

Loading...