USB on-the-go full-speed (OTG_FS) RM0008

872/1096 Doc ID 13902 Rev 12

OTG device endpoint-x control register (OTG_FS_DIEPCTLx) (x = 1..3, where

x = Endpoint_number)

Address offset: 0x900 + (Endpoint_number × 0x20)

Reset value: 0x0000 0000

The application uses this register to control the behavior of each logical endpoint other than

endpoint 0.

Bit 17 NAKSTS: NAK status

Indicates the following:

0: The core is transmitting non-NAK handshakes based on the FIFO status

1: The core is transmitting NAK handshakes on this endpoint.

When this bit is set, either by the application or core, the core stops transmitting data, even if

there are data available in the TxFIFO. Irrespective of this bit’s setting, the core always

responds to SETUP data packets with an ACK handshake.

Bit 16 Reserved

Bit 15 USBAEP: USB active endpoint

This bit is always set to 1, indicating that control endpoint 0 is always active in all

configurations and interfaces.

Bits 14:2 Reserved

Bits 1:0 MPSIZ: Maximum packet size

The application must program this field with the maximum packet size for the current logical

endpoint.

00: 64 bytes

01: 32 bytes

10: 16 bytes

11: 8 bytes

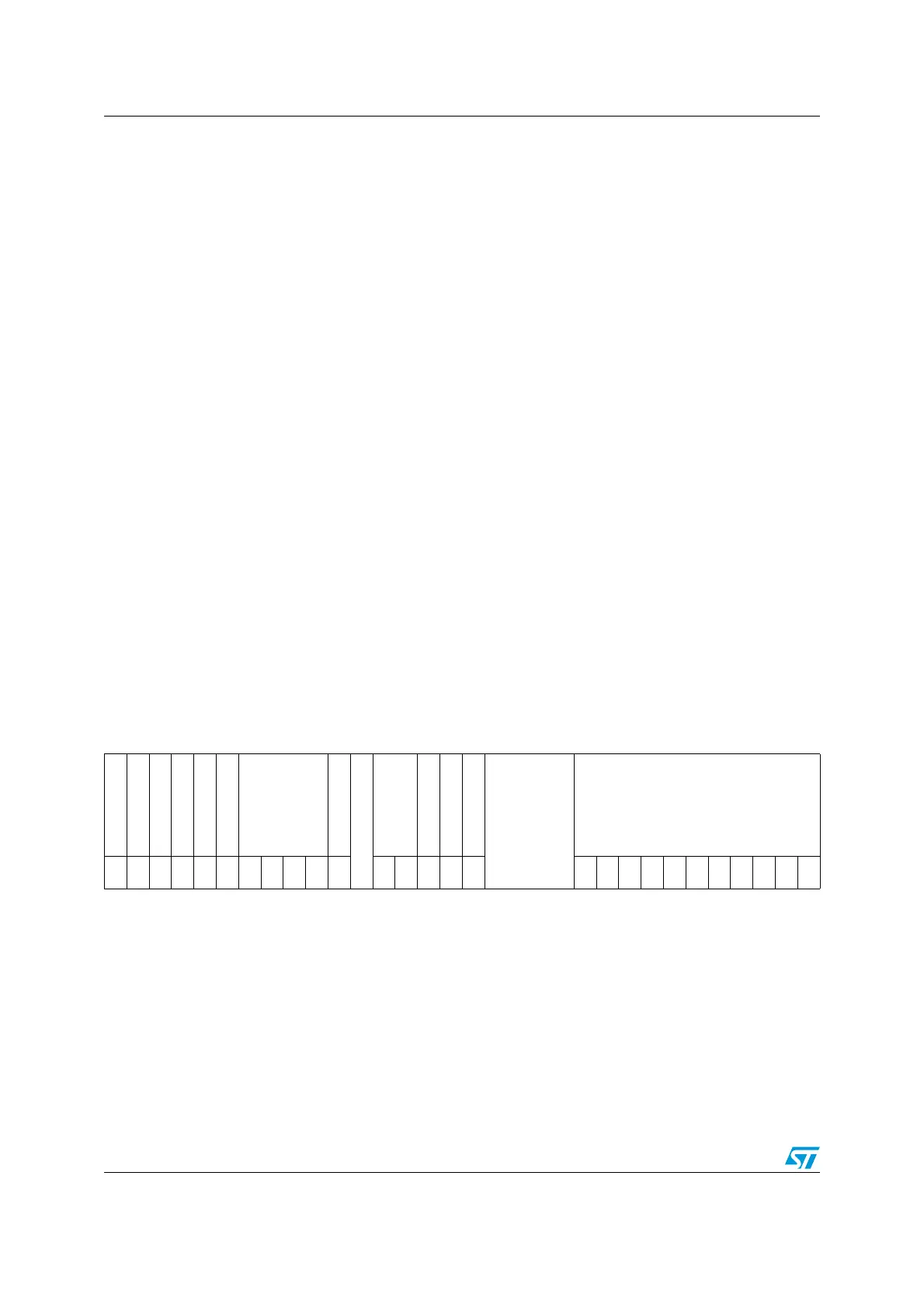

313029282726252423222120191817161514131211109876543210

EPENA

EPDIS

SODDFRM

SD0PID/SEVNFRM

SNAK

CNAK

TXFNUM

Stall

Reserved

EPTYP

NAKSTS

EONUM/DPID

USBAEP

Reserved

MPSIZ

rsrswwwwrwrwrwrw

rw/

rs

rw rw r r rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 EPENA: Endpoint enable

The application sets this bit to start transmitting data on an endpoint.

The core clears this bit before setting any of the following interrupts on this endpoint:

– SETUP phase done

– Endpoint disabled

– Transfer completed

Loading...

Loading...