RM0008 Ethernet (ETH): media access control (MAC) with DMA controller

Doc ID 13902 Rev 12 1029/1096

Ethernet DMA bus mode register (ETH_DMABMR)

Address offset: 0x1000

Reset value: 0x0000 2101

The bus mode register establishes the bus operating modes for the DMA.

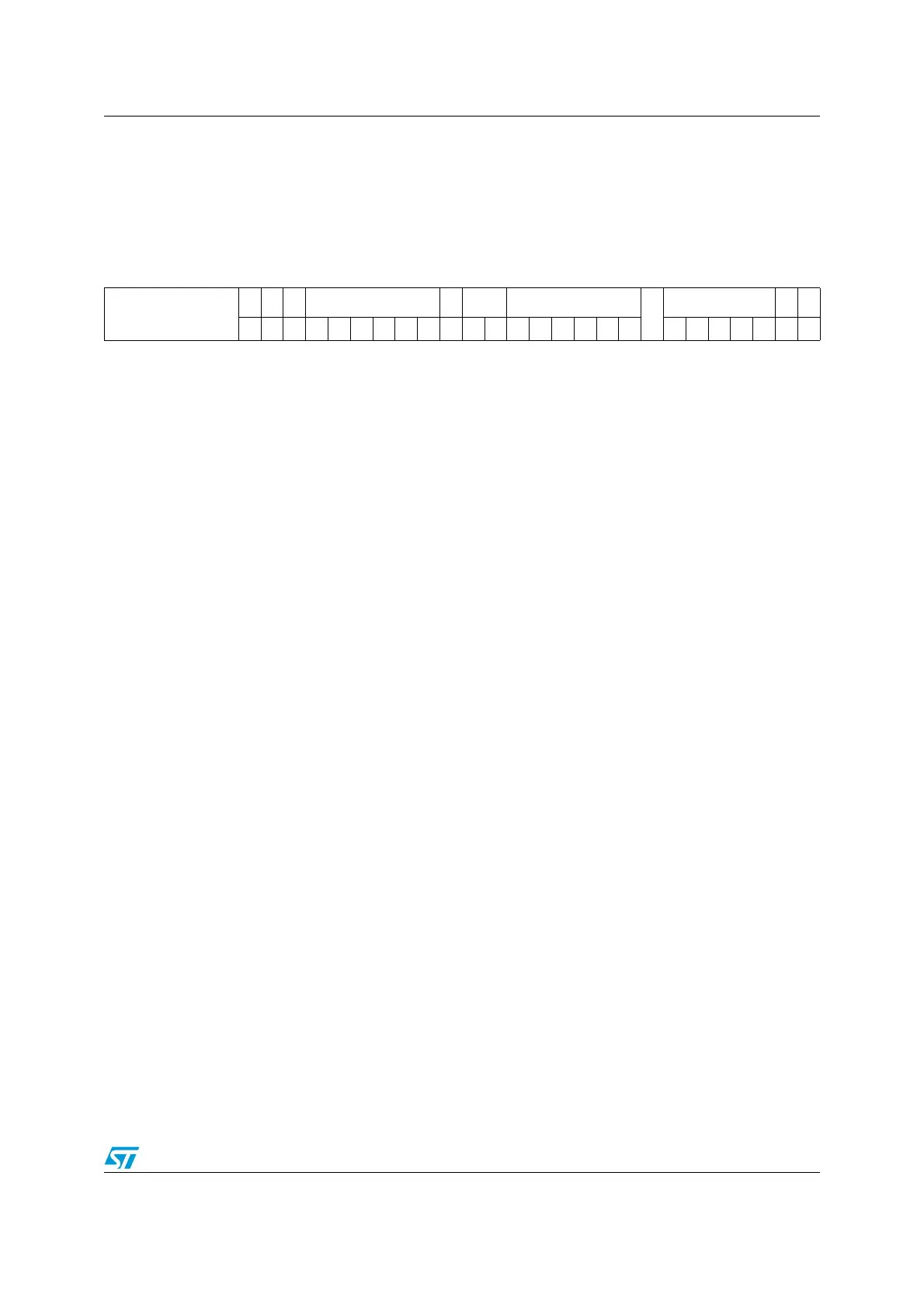

313029282726252423222120191817161514131211109876543210

Reserved

AAB

FPM

USP

RDP

FB

RTPR PBL

Reserved

DSL

DA

SR

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rs

Bits 31:26 Reserved

Bit 25 AAB: Address-aligned beats

When this bit is set high and the FB bit equals 1, the AHB interface generates all bursts aligned

to the start address LS bits. If the FB bit equals 0, the first burst (accessing the data buffer’s

start address) is not aligned, but subsequent bursts are aligned to the address.

Bit 24 FPM: 4xPBL mode

When set high, this bit multiplies the PBL value programmed (bits [22:17] and bits [13:8]) four

times. Thus the DMA transfers data in a maximum of 4, 8, 16, 32, 64 and 128 beats depending

on the PBL value.

Bit 23 USP: Use separate PBL

When set high, it configures the RxDMA to use the value configured in bits [22:17] as PBL

while the PBL value in bits [13:8] is applicable to TxDMA operations only. When this bit is

cleared, the PBL value in bits [13:8] is applicable for both DMA engines.

Bits 22:17 RDP: Rx DMA PBL

These bits indicate the maximum number of beats to be transferred in one RxDMA transaction.

This is the maximum value that is used in a single block read/write operation. The RxDMA

always attempts to burst as specified in RDP each time it starts a burst transfer on the host

bus. RDP can be programmed with permissible values of 1, 2, 4, 8, 16, and 32. Any other value

results in undefined behavior.

These bits are valid and applicable only when USP is set high.

Bit 16 FB: Fixed burst

This bit controls whether the AHB Master interface performs fixed burst transfers or not. When

set, the AHB uses only SINGLE, INCR4, INCR8 or INCR16 during start of normal burst

transfers. When reset, the AHB uses SINGLE and INCR burst transfer operations.

Bits 15:14 RTPR: Rx Tx priority ratio

RxDMA requests are given priority over TxDMA requests in the following ratio:

00: 1:1

01: 2:1

10: 3:1

11: 4:1

This is valid only when the DA bit is cleared.

Loading...

Loading...