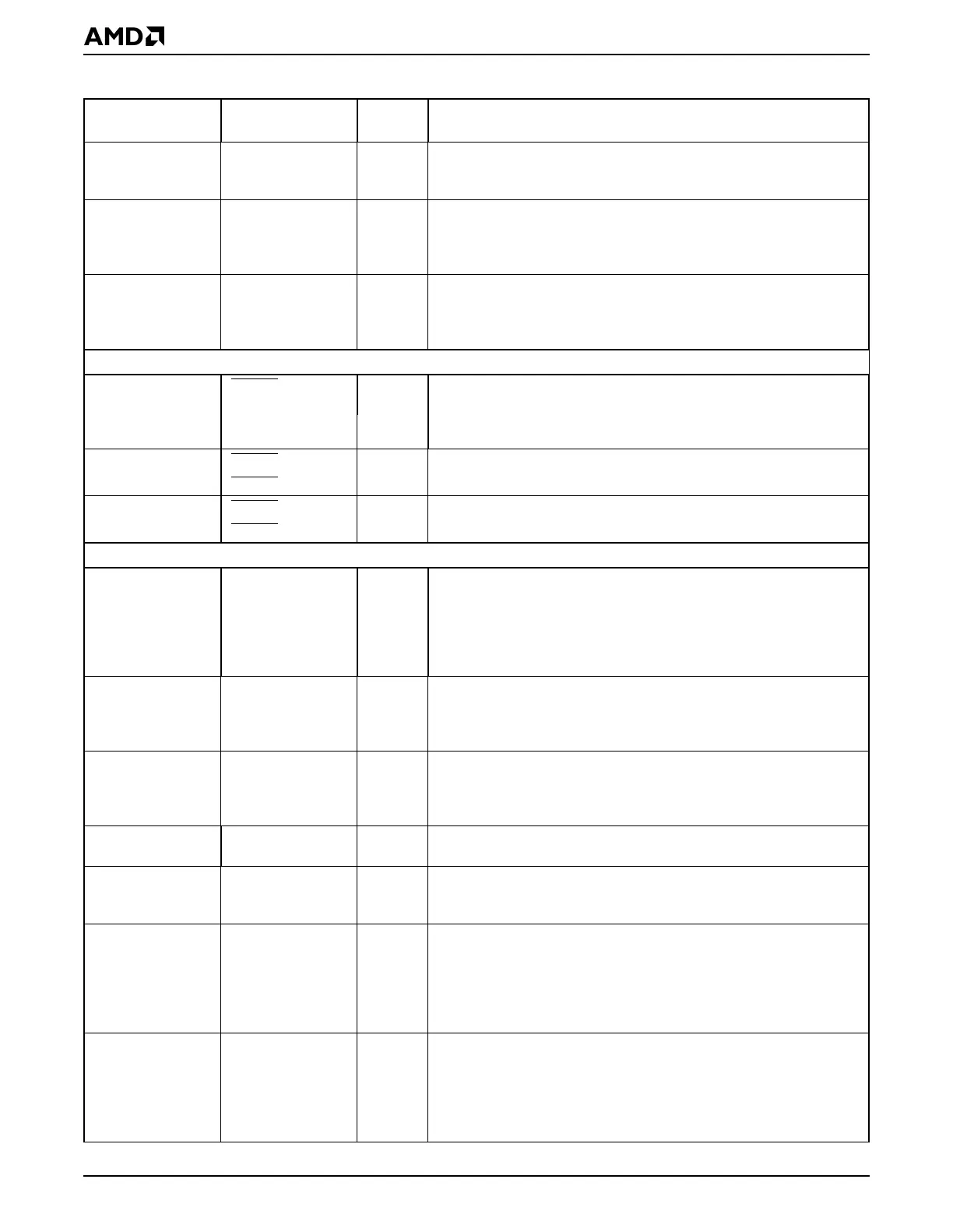

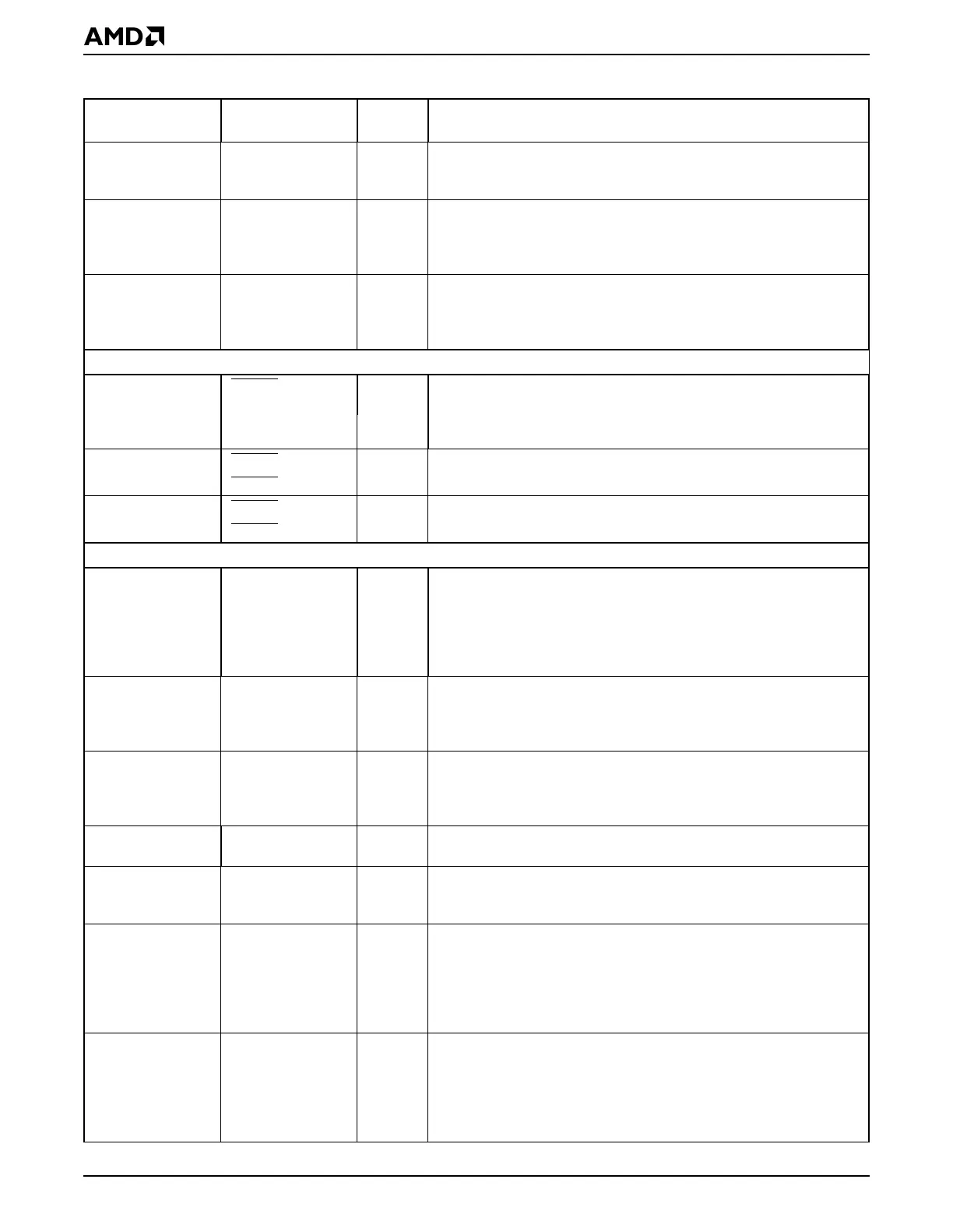

Pin Information

2-10 Élan™SC520 Microcontroller User’s Manual

SSI_CLK —OSSI Clock is driven by the ÉlanSC520 microcontroller SSI port during

active SSI transmit or receive transactions. The idle state of the clock

and the assertion/sample edge are configurable.

SSI_DI — STI SSI Data Input receives incoming data from a peripheral device SSI

port. Data is shifted in on the opposite SSI_CLK signal edge in which

SSI_DO drives data. SSI_DO and SSI_DI can be tied together to

interface to a three-pin SSI peripheral.

SSI_DO — OD SSI Data Output drives data to a peripheral device SSI port. Data is

driven on the opposite SSI_CLK signal edge in which SSI_DI latches

data. The DO signal is normally at high-impedance when no transmit

transaction is active on the SSI port.

Timers

PITGATE2 [GPCS3]IProgrammable Interval Timer 2 Gate provides control for the PIT

Channel 2.

Programmable Interval Timer 2 Output is output from the PIT

Channel 2. This signal is typically used as the PC speaker signal.

PITOUT2 {CFG3} O

TMRIN0 [GPCS5

]ITimer Inputs 0 and 1 can be programmed to be the control or clock

for the general-purpose (GP) timers 0 and 1.

TMRIN1 [GPCS4

]I

TMROUT0 [GPCS7

]OTimer Outputs 0 and 1 are outputs from two of the GP timers. These

outputs can be used as pulse-width modulation signals.

TMROUT1 [GPCS6

]O

Clocks and Reset

32KXTAL2–

32KXTAL1

—osc32.768-kHz Crystal Interface is used for connecting an external

crystal or oscillator to the ÉlanSC520 microcontroller. This clock

source is used to clock the real-time clock (RTC). In addition, internal

PLLs generate clocks for the timers and UARTs based on this clock

source. When an external oscillator is used, 32KXTAL1 should be

unconnected and the clock source driven on 32KXTAL2.

33MXTAL2–

33MXTAL1

—osc33-MHz Crystal Interface is the main system clock for the chip. This

clock source is used to derive the SDRAM, CPU, and PCI clocks.

When an external oscillator is used, 33MXTAL1 should be grounded

and the clock source driven on 33MXTAL2.

[CLKTEST] CLKTIMER O Test Clock Output is a shared pin that allows many of the internal

clocks to be driven externally. CLKTEST can drive the internal clocks

of the UARTs, PLL1, PLL2, the programmable interval timer (PIT), or

the real-time clock (RTC) for testing or for driving an external device.

CLKTIMER [CLKTEST] I Timer Clock Input is a shared clock pin that can be used to input a

frequency to the programmable interval timer (PIT).

LF_PLL1 — I Loop Filter Interface is used for connecting external loop filter

components. Component values and circuit descriptions are contained

in the

Élan™SC520 Microcontroller Data Sheet

, order #22003.

PRGRESET —STIProgrammable Reset can be programmed to reset the ÉlanSC520

microcontroller, but allow SDRAM refresh to continue during the reset.

This allows the system to be reset without losing the information stored

in SDRAM. On power-up, PRGRESET is disabled and must be

programmed to be operational. When disabled, this pin has no effect

on the ÉlanSC520 microcontroller.

PWRGOOD — STI Power Good is a reset signal that indicates to the ÉlanSC520

microcontroller that the V

CC

levels are within the normal operation

range. It is used to reset the entire chip and must be held Low for one

second after all V

CC

signals (except VCC_RTC) on the chip are High.

This signal must be returned Low before the V

CC

signals degrade to

put the RTC into the correct state for operation in RTC-only mode.

Table 2-2 Signal Descriptions (Continued)

Signal

Multiplexed

Signal Type Description

Loading...

Loading...