RM0008 General-purpose and alternate-function I/Os (GPIOs and AFIOs)

Doc ID 13902 Rev 12 181/1096

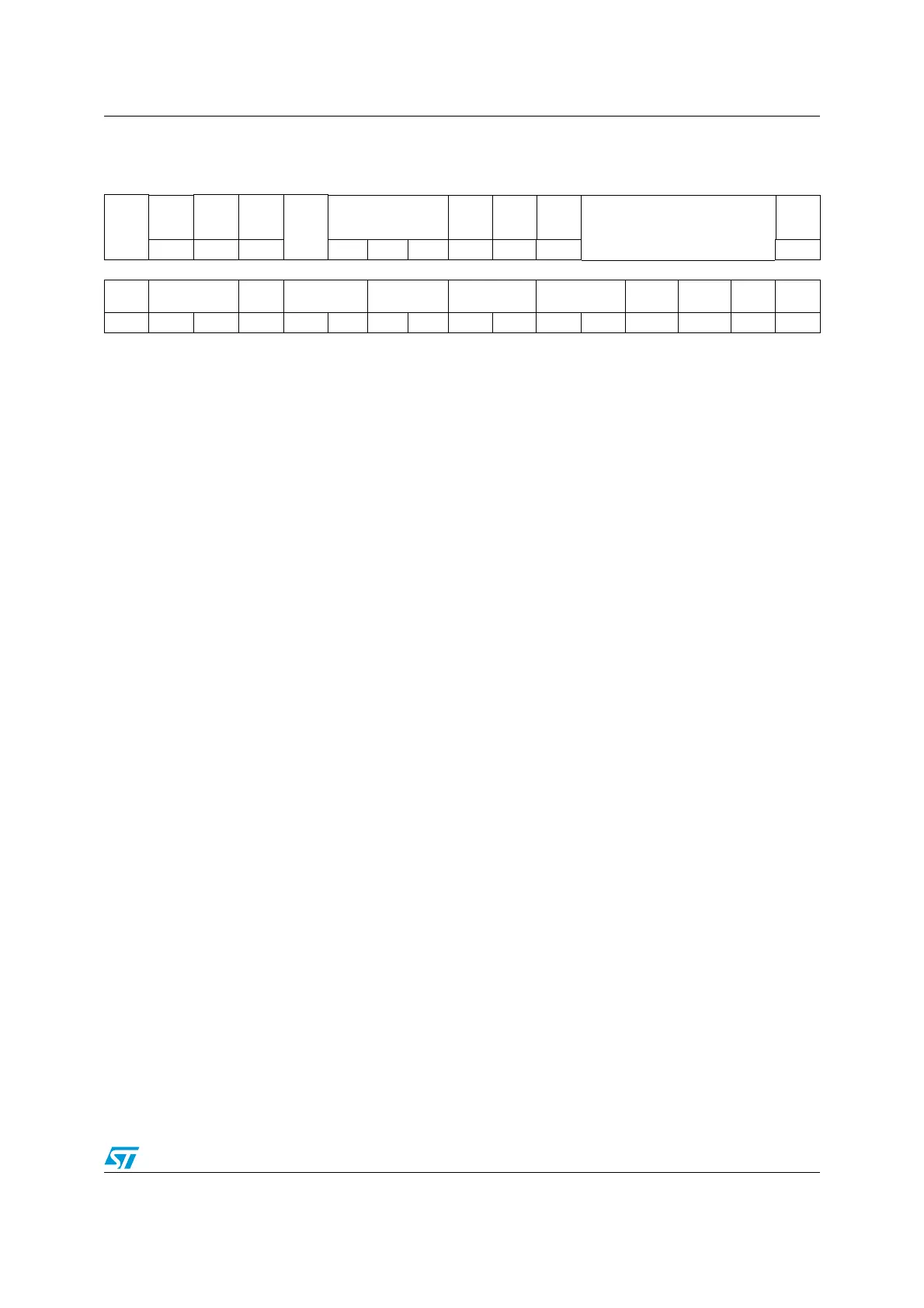

Memory map and bit definitions for connectivity line devices:

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

PTP_P

PS_RE

MAP

TIM2ITR

1_

IREMAP

SPI3_

REMAP

Res.

SWJ_

CFG[2:0]

MII_RMI

I_SEL

CAN2_

REMAP

ETH_R

EMAP

Reserved

TIM5CH

4_IREM

AP

rw rw rw w w w rw rw rw rw

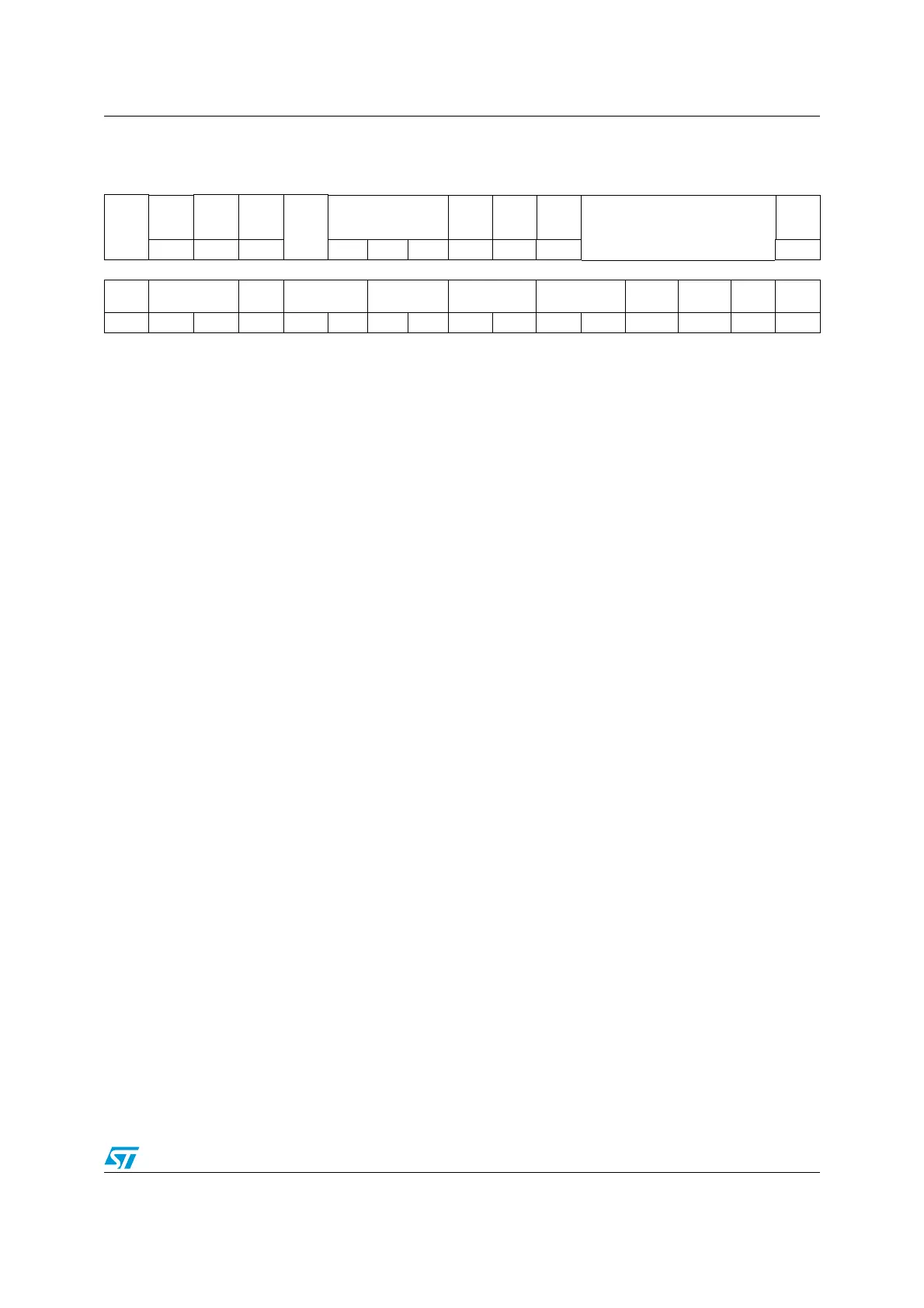

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PD01_

REMAP

CAN1_REMAP

[1:0]

TIM4_

REMAP

TIM3_REMAP

[1:0]

TIM2_REMAP

[1:0]

TIM1_REMAP

[1:0]

USART3_

REMAP[1:0]

USART2_

REMAP

USART1_

REMAP

I2C1_

REMAP

SPI1_

REMAP

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 Reserved

Bit 30 PTP_PPS_REMAP: Ethernet PTP PPS remapping

This bit is set and cleared by software. It enables the Ethernet MAC PPS_PTS to be output

on the PB5 pin.

0: PTP_PPS not output on PB5 pin.

1: PTP_PPS is output on PB5 pin.

Note: This bit is available only in connectivity line devices and is reserved otherwise.

Bit 29 TIM2ITR1_IREMAP: TIM2 internal trigger 1 remapping

This bit is set and cleared by software. It controls the TIM2_ITR1 internal mapping.

0: Connect TIM2_ITR1 internally to the Ethernet PTP output for calibration purposes.

1: Connect USB OTG SOF (Start of Frame) output to TIM2_ITR1 for calibration purposes.

Note: This bit is available only in connectivity line devices and is reserved otherwise.

Bit 28 SPI3_REMAP: SPI3/I2S3 remapping

This bit is set and cleared by software. It controls the mapping of SPI3_NSS/I2S3_WS,

SPI3_SCK/I2S3_CK, SPI3_MISO, SPI3_MOSI/I2S3_SD alternate functions on the GPIO

ports.

0: No remap (SPI_NSS-I2S3_WS/PA15, SPI3_SCK-I2S3_CK/PB3, SPI3_MISO/PB4,

SPI3_MOSI-I2S3_SD/PB5)

1: Remap (SPI3_NSS-I2S3_WS/PA4, SPI3_SCK-I2S3_CK/PC10, SPI3_MISO/PC11,

SPI3_MOSI-I2S3_SD/PC12)

Note: This bit is available only in connectivity line devices and is reserved otherwise.

Bit 27 Reserved

Bits 26:24 SWJ_CFG[2:0]: Serial wire JTAG configuration

These bits are write-only (when read, the value is undefined). They are used to configure the

SWJ and trace alternate function I/Os. The SWJ (Serial Wire JTAG) supports JTAG or SWD

access to the Cortex debug port. The default state after reset is SWJ ON without trace. This

allows JTAG or SW mode to be enabled by sending a specific sequence on the JTMS /

JTCK pin.

000: Full SWJ (JTAG-DP + SW-DP): Reset State

001: Full SWJ (JTAG-DP + SW-DP) but without NJTRST

010: JTAG-DP Disabled and SW-DP Enabled

100: JTAG-DP Disabled and SW-DP Disabled

Other combinations: no effect

Bit 23 MII_RMII_SEL: MII or RMII selection

This bit is set and cleared by software. It configures the Ethernet MAC internally for use with

an external MII or RMII PHY.

0: Configure Ethernet MAC for connection with an MII PHY

1: Configure Ethernet MAC for connection with an RMII PHY

Note: This bit is available only in connectivity line devices and is reserved otherwise.

Loading...

Loading...