Universal serial bus full-speed device interface (USB) RM0008

616/1096 Doc ID 13902 Rev 12

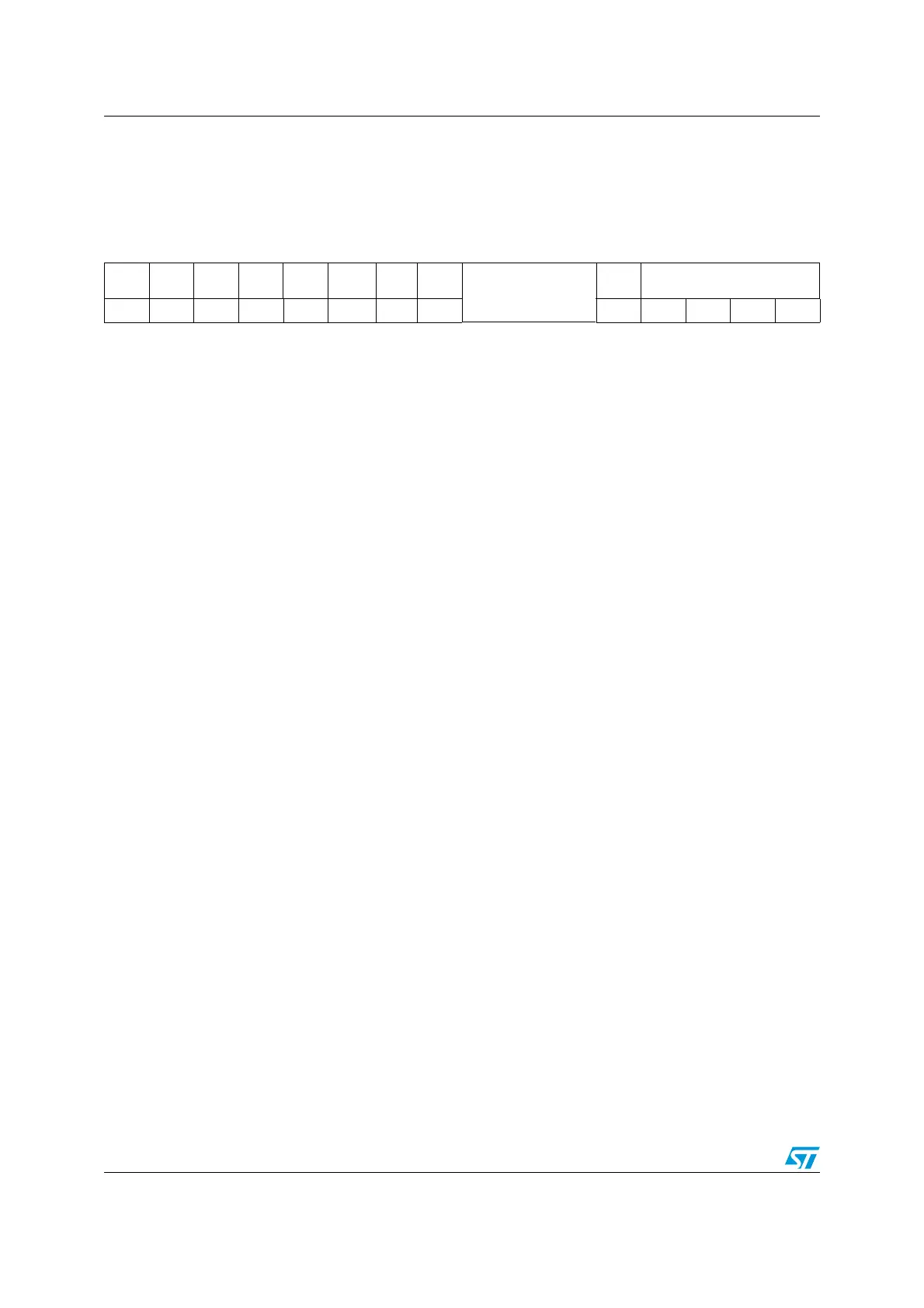

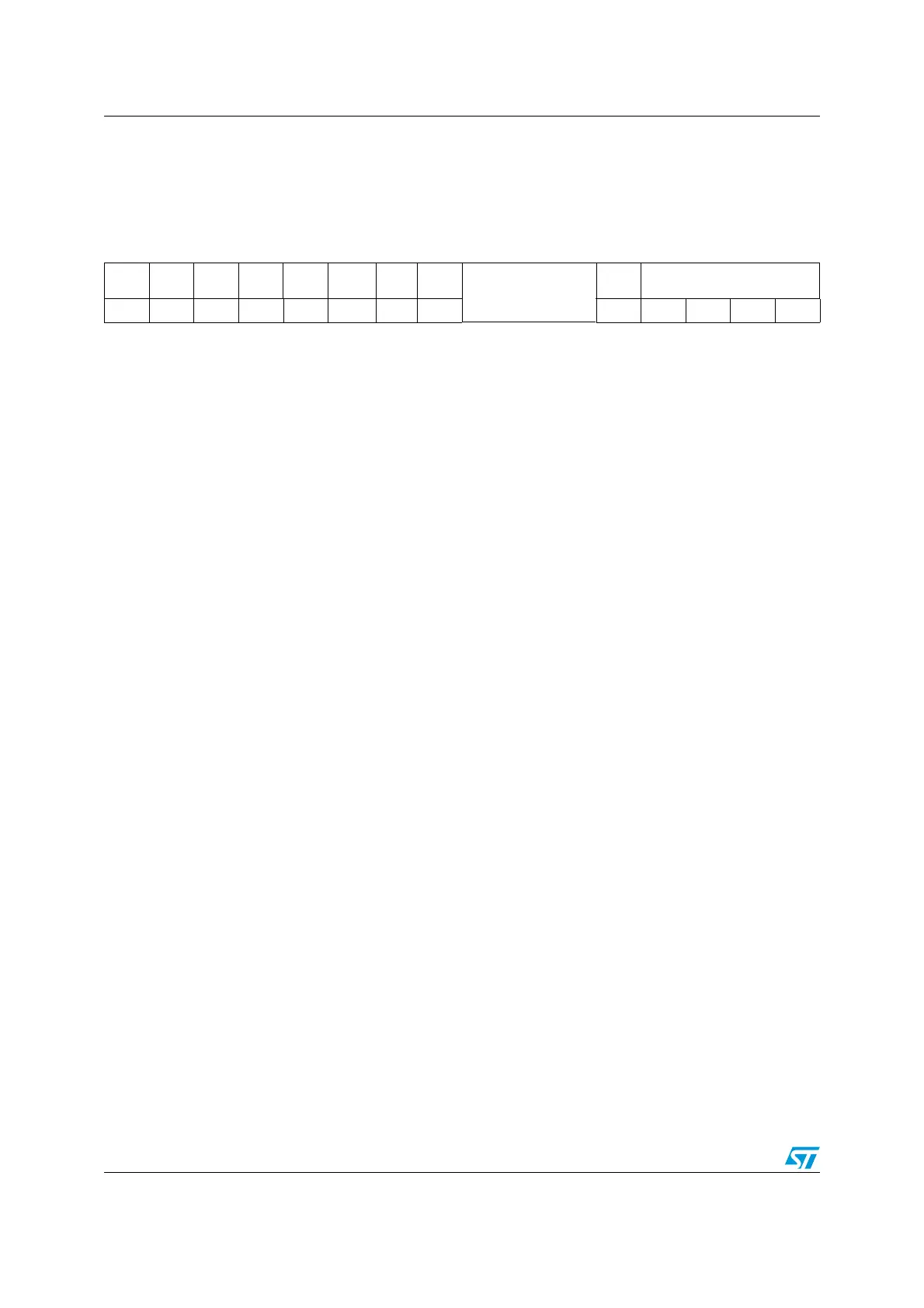

USB interrupt status register (USB_ISTR)

Address offset: 0x44

Reset value: 0x0000 0000

This register contains the status of all the interrupt sources allowing application software to

determine, which events caused an interrupt request.

The upper part of this register contains single bits, each of them representing a specific

event. These bits are set by the hardware when the related event occurs; if the

corresponding bit in the USB_CNTR register is set, a generic interrupt request is generated.

The interrupt routine, examining each bit, will perform all necessary actions, and finally it will

clear the serviced bits. If any of them is not cleared, the interrupt is considered to be still

pending, and the interrupt line will be kept high again. If several bits are set simultaneously,

only a single interrupt will be generated.

Endpoint transaction completion can be handled in a different way to reduce interrupt

response latency. The CTR bit is set by the hardware as soon as an endpoint successfully

completes a transaction, generating a generic interrupt request if the corresponding bit in

USB_CNTR is set. An endpoint dedicated interrupt condition is activated independently

from the CTRM bit in the USB_CNTR register. Both interrupt conditions remain active until

software clears the pending bit in the corresponding USB_EPnR register (the CTR bit is

actually a read only bit). For endpoint-related interrupts, the software can use the Direction

of Transaction (DIR) and EP_ID read-only bits to identify, which endpoint made the last

interrupt request and called the corresponding interrupt service routine.

The user can choose the relative priority of simultaneously pending USB_ISTR events by

specifying the order in which software checks USB_ISTR bits in an interrupt service routine.

Only the bits related to events, which are serviced, are cleared. At the end of the service

routine, another interrupt will be requested, to service the remaining conditions.

To avoid spurious clearing of some bits, it is recommended to clear them with a load

instruction where all bits which must not be altered are written with 1, and all bits to be

cleared are written with ‘0 (these bits can only be cleared by software). Read-modify-write

cycles should be avoided because between the read and the write operations another bit

could be set by the hardware and the next write will clear it before the microprocessor has

the time to serve the event.

1514131211109876543210

CTR

PMA

OVR

ERR WKUP SUSP RESET SOF ESOF

Reserved

DIR EP_ID[3:0]

rrc_w0rc_w0rc_w0rc_w0rc_w0rc_w0rc_w0 rrrrr

Loading...

Loading...