Universal serial bus full-speed device interface (USB) RM0008

626/1096 Doc ID 13902 Rev 12

Transmission byte count n (USB_COUNTn_TX)

Address offset: [USB_BTABLE] + n*16 + 4

USB local Address: [USB_BTABLE] + n*8 + 2

Note: Double-buffered and Isochronous IN Endpoints have two USB_COUNTn_TX

registers: named USB_COUNTn_TX_1 and USB_COUNTn_TX_0 with the

following content.

Reception buffer address n (USB_ADDRn_RX)

Address offset: [USB_BTABLE] + n*16 + 8

USB local Address: [USB_BTABLE] + n*8 + 4

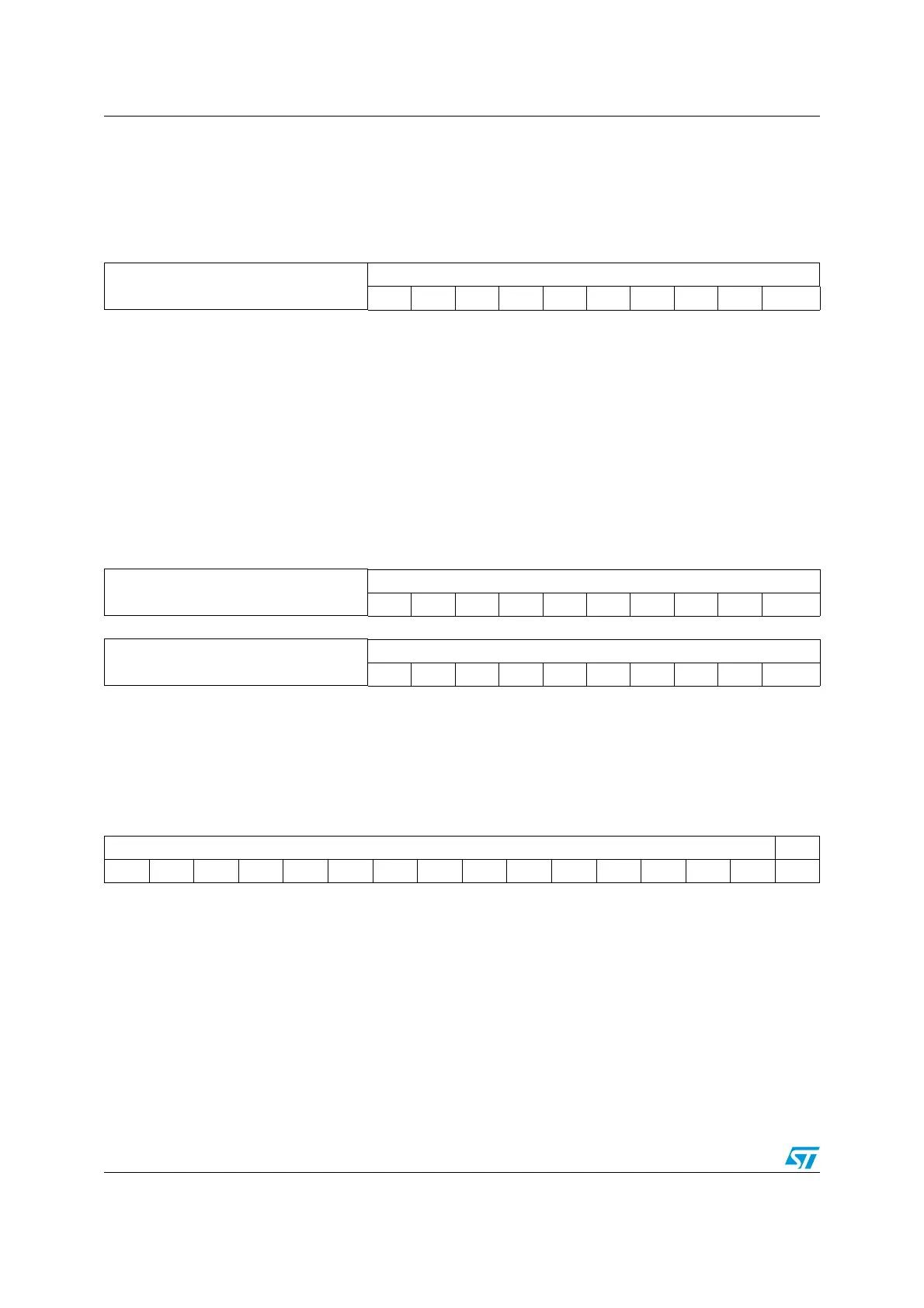

151413121110987654321 0

Reserved

COUNTn_TX[9:0]

rw rw rw rw rw rw rw rw rw rw

Bits 15:10 These bits are not used since packet size is limited by USB specifications to 1023 bytes. Their

value is not considered by the USB peripheral.

Bits 9:0 COUNTn_TX[9:0]: Transmission byte count

These bits contain the number of bytes to be transmitted by the endpoint associated with the

USB_EPnR register at the next IN token addressed to it.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

COUNTn_TX_1[9:0]

rw rw rw rw rw rw rw rw rw rw

151413121110987654321 0

Reserved

COUNTn_TX_0[9:0]

rw rw rw rw rw rw rw rw rw rw

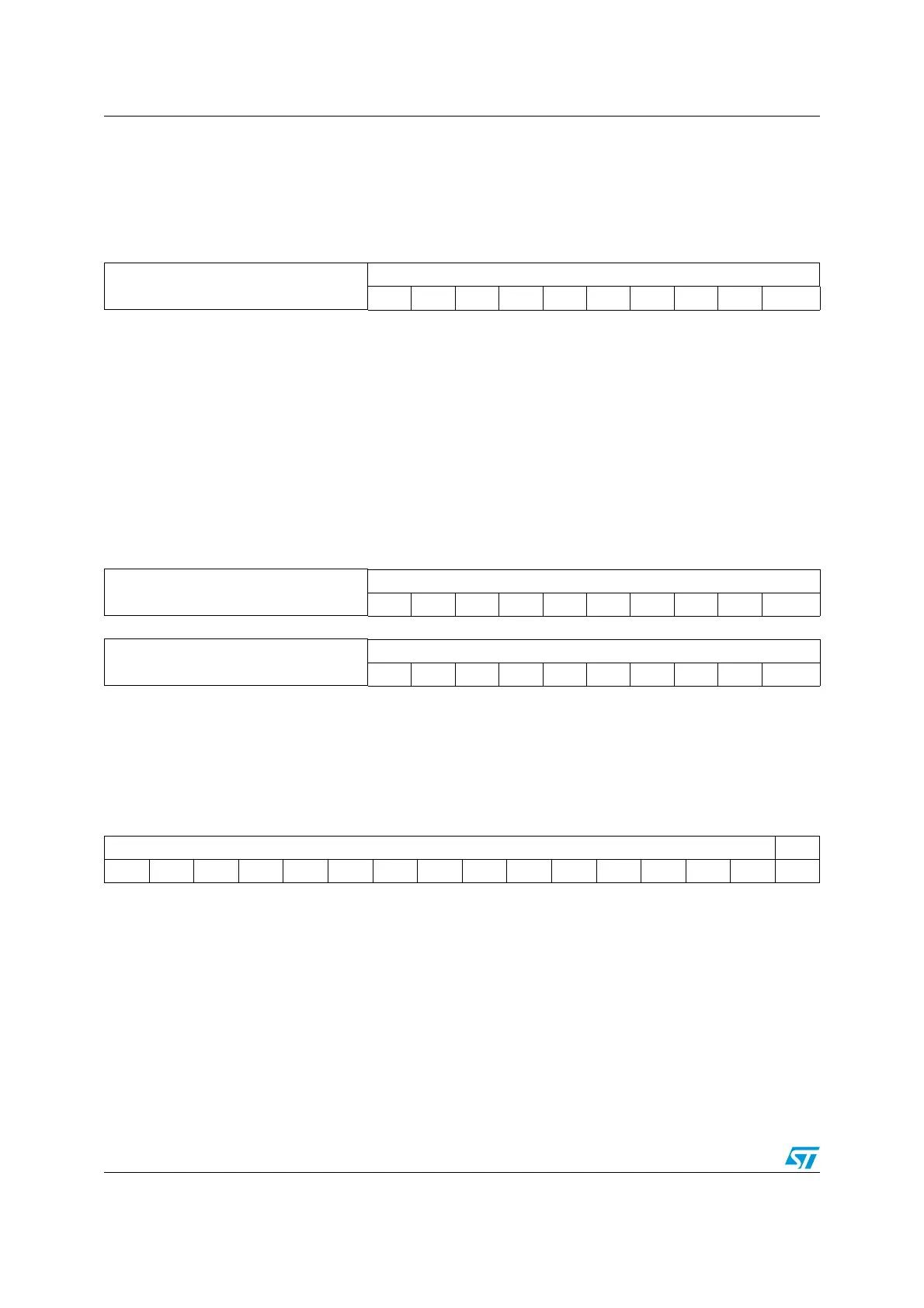

1514131211109876543210

ADDRn_RX[15:1] -

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw -

Bits 15:1 ADDRn_RX[15:1]: Reception buffer address

These bits point to the starting address of the packet buffer, which will contain the data

received by the endpoint associated with the USB_EPnR register at the next OUT/SETUP

token addressed to it.

Bit 0 This bit must always be written as ‘0 since packet memory is word-wide and all packet buffers

must be word-aligned.

Loading...

Loading...