USB on-the-go full-speed (OTG_FS) RM0008

860/1096 Doc ID 13902 Rev 12

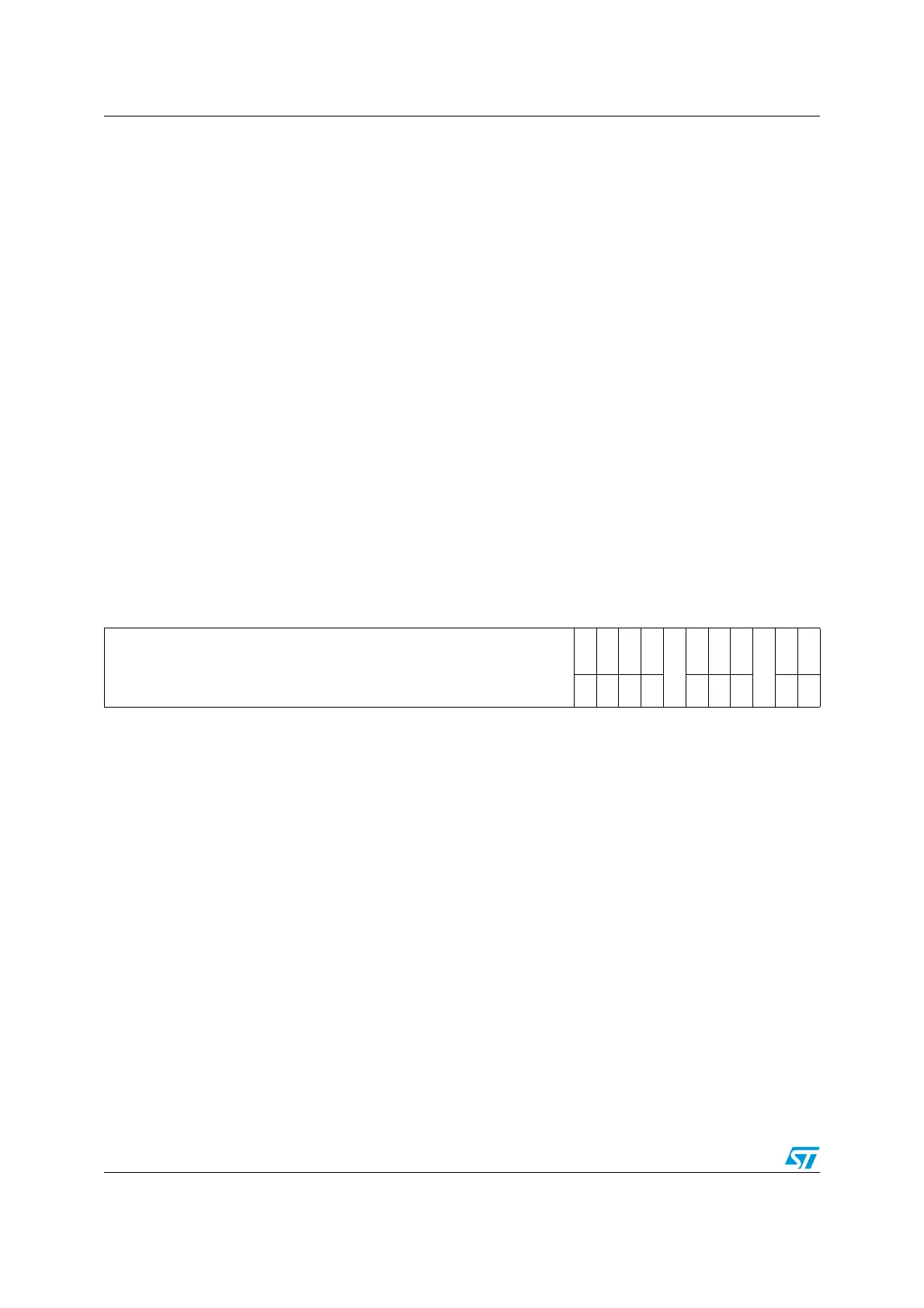

OTG_FS Host channel-x interrupt register (OTG_FS_HCINTx) (x = 0..7, where

x = Channel_number)

Address offset: 0x508 + (Channel_number × 0x20)

Reset value: 0x0000 0000

This register indicates the status of a channel with respect to USB- and AHB-related events.

It is shown in Figure 309. The application must read this register when the host channels

interrupt bit in the Core interrupt register (HCINT bit in OTG_FS_GINTSTS) is set. Before

the application can read this register, it must first read the host all channels interrupt

(OTG_FS_HAINT) register to get the exact channel number for the host channel-x interrupt

register. The application must clear the appropriate bit in this register to clear the

corresponding bits in the OTG_FS_HAINT and OTG_FS_GINTSTS registers.

Bit 15 EPDIR: Endpoint direction

Indicates whether the transaction is IN or OUT.

0: OUT

1: IN

Bits 14:11 EPNUM: Endpoint number

Indicates the endpoint number on the device serving as the data source or sink.

Bits 10:0 MPSIZ: Maximum packet size

Indicates the maximum packet size of the associated endpoint.

313029282726252423222120191817161514131211109876543210

Reserved

DTERR

FRMOR

BBERR

TXERR

Reserved

ACK

NAK

STALL

Reserved

CHH

XFRC

rc_

w1

rc_

w1

rc_

w1

rc_

w1

rc_

w1

rc_

w1

rc_

w1

rc_

w1

rc_

w1

Bits 31:11 Reserved

Bit 10 DTERR: Data toggle error

Bit 9 FRMOR: Frame overrun

Bit 8 BBERR: Babble error

Bit 7 TXERR: Transaction error

Indicates one of the following errors occurred on the USB.

CRC check failure

Timeout

Bit stuff error

False EOP

Bit 6 Reserved

Bit 5 ACK: ACK response received/transmitted interrupt

Bit 4 NAK: NAK response received interrupt

Bit 3 STALL: STALL response received interrupt

Loading...

Loading...