Secure digital input/output interface (SDIO) RM0090

1062/1749 RM0090 Rev 18

Note: While the SD/SDIO card or MultiMediaCard is in identification mode, the SDIO_CK

frequency must be less than 400 kHz.

The clock frequency can be changed to the maximum card bus frequency when relative

card addresses are assigned to all cards.

After a data write, data cannot be written to this register for three SDIOCLK clock periods

plus two PCLK2 clock periods. SDIO_CK can also be stopped during the read wait interval

for SD I/O cards: in this case the SDIO_CLKCR register does not control SDIO_CK.

31.9.3 SDIO argument register (SDIO_ARG)

Address offset: 0x08

Reset value: 0x0000 0000

The SDIO_ARG register contains a 32-bit command argument, which is sent to a card as

part of a command message.

31.9.4 SDIO command register (SDIO_CMD)

Address offset: 0x0C

Reset value: 0x0000 0000

The SDIO_CMD register contains the command index and command type bits. The

command index is sent to a card as part of a command message. The command type bits

control the command path state machine (CPSM).

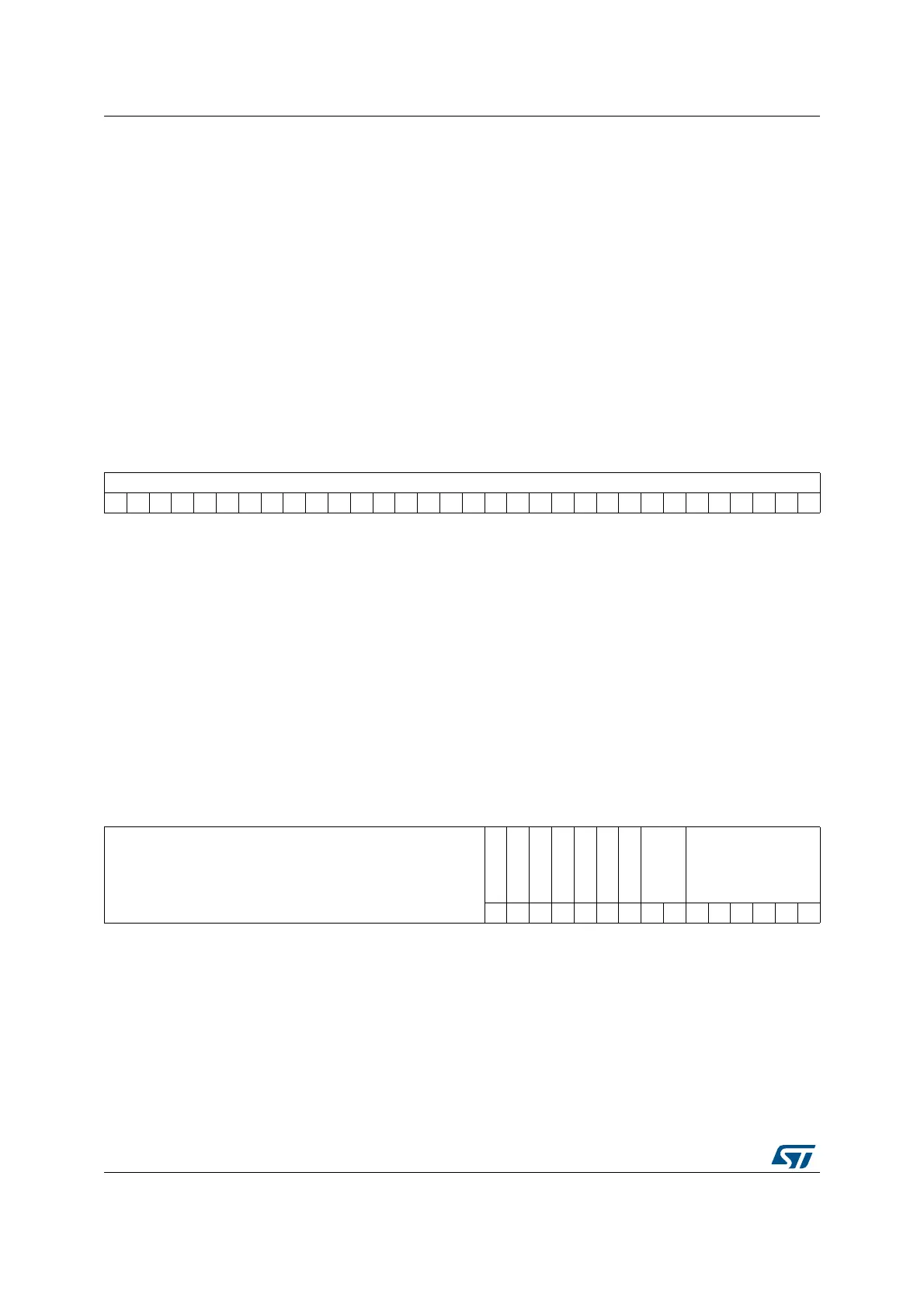

313029282726252423222120191817161514131211109876543210

CMDARG

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 CMDARG: Command argument

Command argument sent to a card as part of a command message. If a command contains

an argument, it must be loaded into this register before writing a command to the command

register.

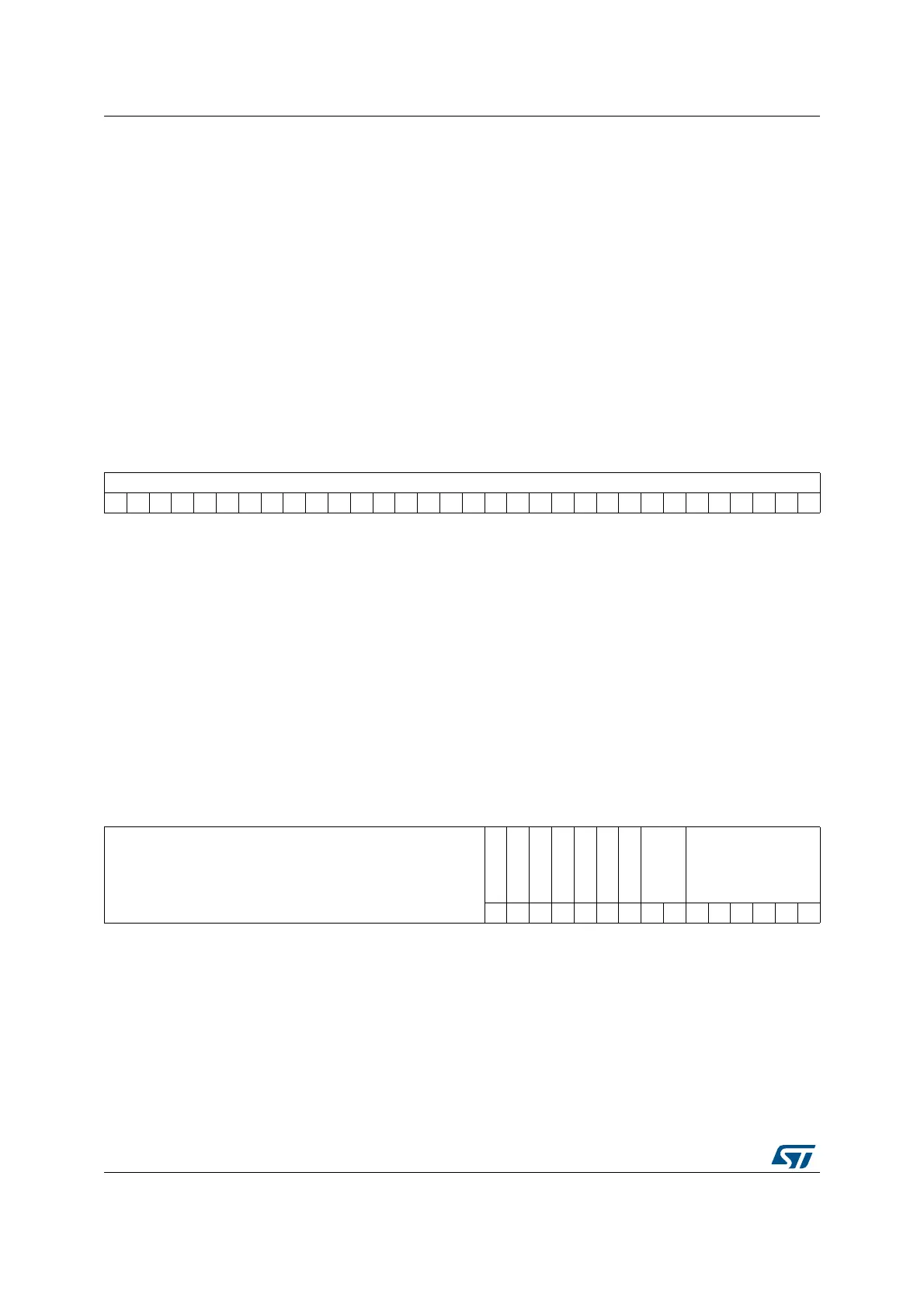

313029282726252423222120191817161514131211109876543210

Reserved

CE-ATACMD

nIEN

ENCMDcompl

SDIOSuspend

CPSMEN

WAITPEND

WAITINT

WAITRESP

CMDINDEX

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:15 Reserved, must be kept at reset value

Bit 14 ATACMD: CE-ATA command

If ATACMD is set, the CPSM transfers CMD61.

Bit 13 nIEN: not Interrupt Enable

if this bit is 0, interrupts in the CE-ATA device are enabled.

Bit 12 ENCMDcompl: Enable CMD completion

If this bit is set, the command completion signal is enabled.

Loading...

Loading...