LCD-TFT controller (LTDC) RM0090

482/1749 RM0090 Rev 18

Care must be taken when accessing the LTDC registers since the APB2 bus is stalling when

the following operations are ongoing:

• Register write access and update for 6 xPCKL2 period + 5x LCD_CLK period (5x

HCLK period for register on AHB clock domain)

• Register read access for 7xPCKL2 period + 5x LCD_CLK period (5x HCLK period for

register on AHB clock domain).

For registers on PCLK2 clock domain, APB2 bus is stalling during the register write access

for 6 xPCKL2 period and 7xPCKL2 period for read access.

The LCD controller can be reset by setting the corresponding bit in the RCC_APB2RSTR

register. It resets the three clock domains.

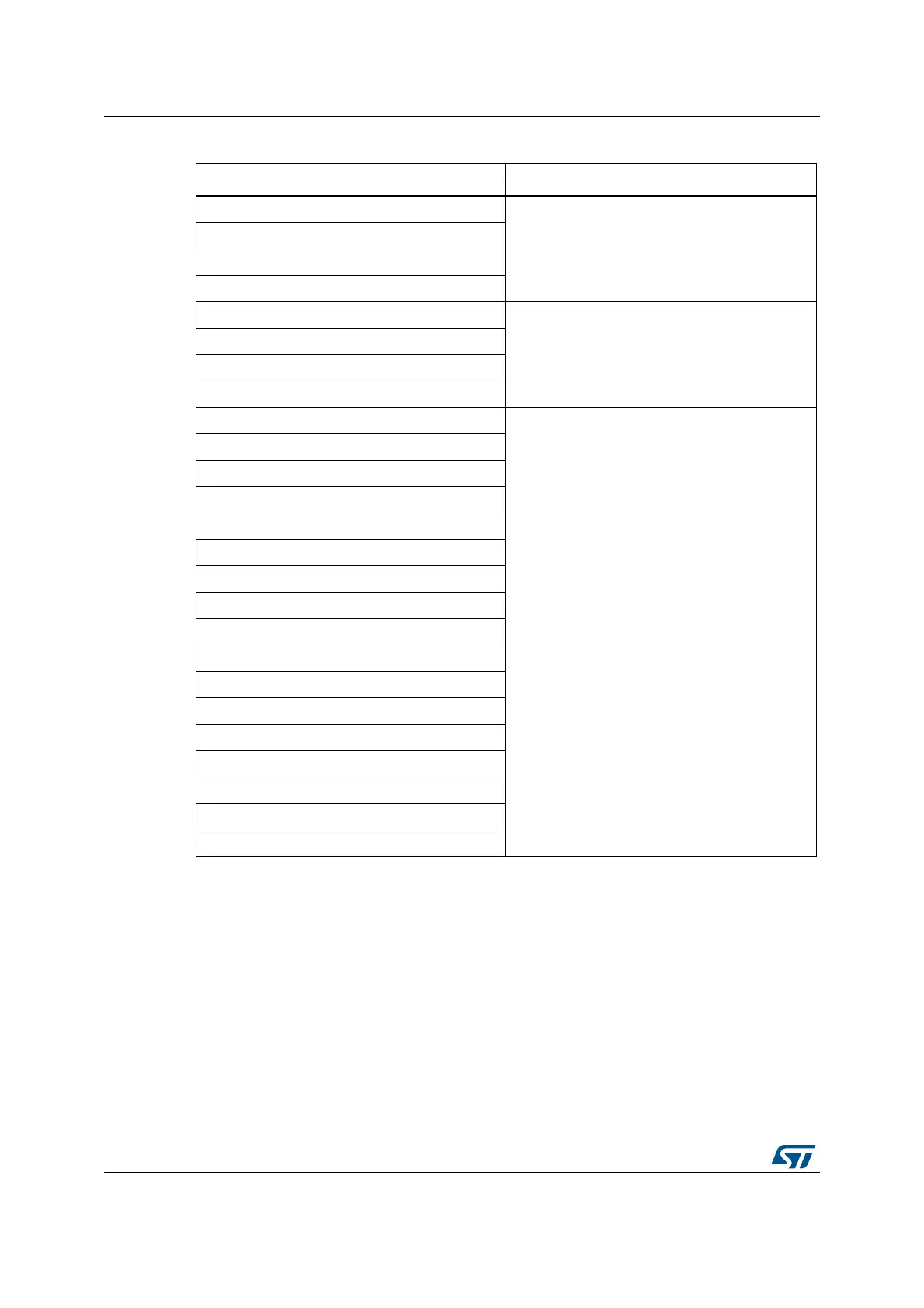

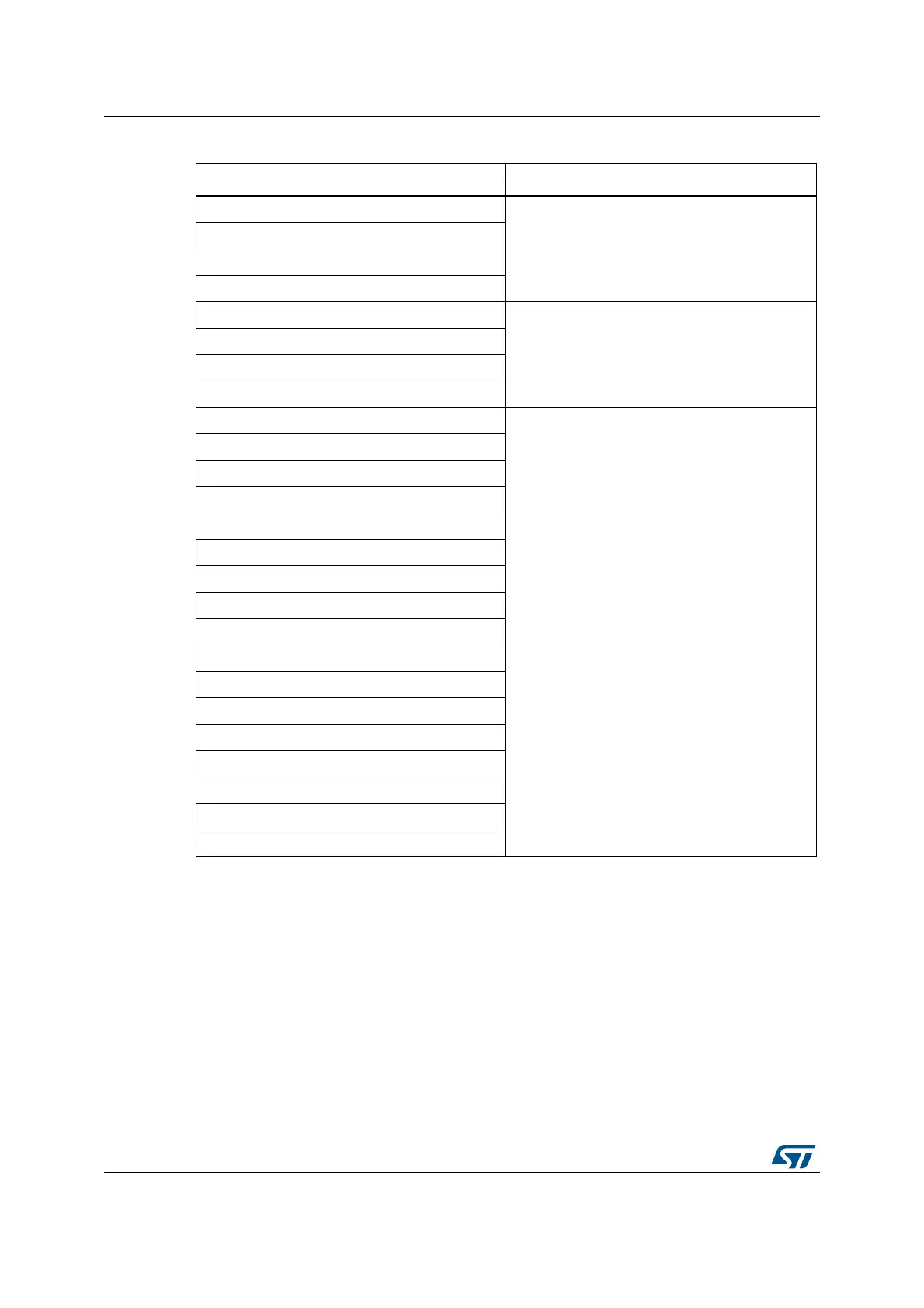

Table 88. LTDC registers versus clock domain

LTDC registers Clock domain

LTDC_LxCR

HCLK

LTDC_LxCFBAR

LTDC_LxCFBLR

LTDC_LxCFBLNR

LTDC_SRCR

PCLK2

LTDC_IER

LTDC_ISR

LTDC_ICR

LTDC_SSCR

Pixel Clock (LCD_CLK)

LTDC_BPCR

LTDC_AWCR

LTDC_TWCR

LTDC_GCR

LTDC_BCCR

LTDC_LIPCR

LTDC_CPSR

LTDC_CDSR

LTDC_LxWHPCR

LTDC_LxWVPCR

LTDC_LxCKCR

LTDC_LxPFCR

LTDC_LxCACR

LTDC_LxDCCR

LTDC_LxBFCR

LTDC_LxCLUTWR

Loading...

Loading...