RM0090 Rev 18 1667/1749

RM0090 Flexible memory controller (FMC)

1682

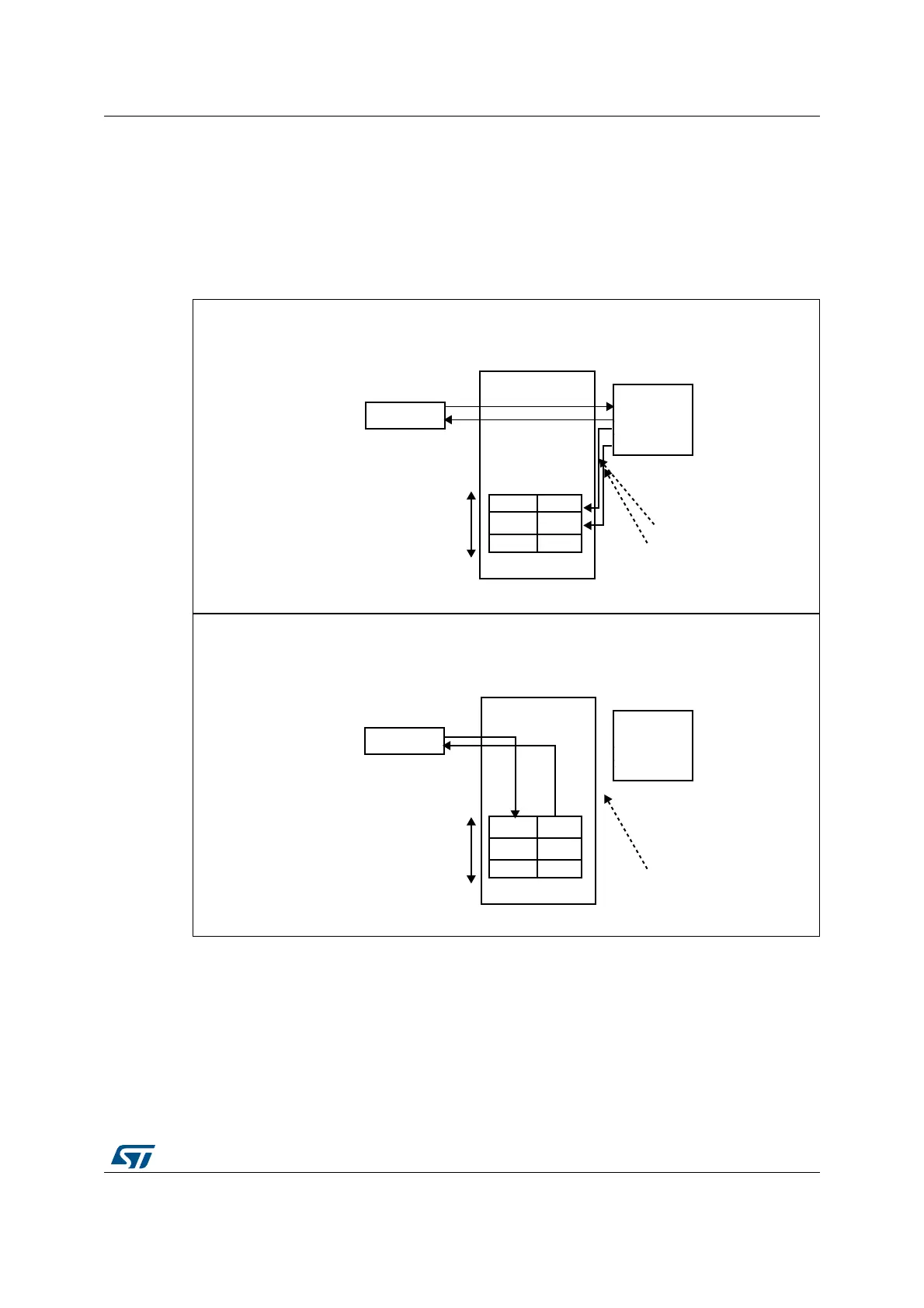

Each time a read request occurs, the SDRAM controller checks:

• If the address matches one of the address tags, data are directly read from the FIFO

and the corresponding address tag/ line content is cleared and the remaining data in

the FIFO are compacted to avoid empty lines.

• Otherwise, a new read command is issued to the memory and the FIFO is updated with

new data. If the FIFO is full, the older data are lost.

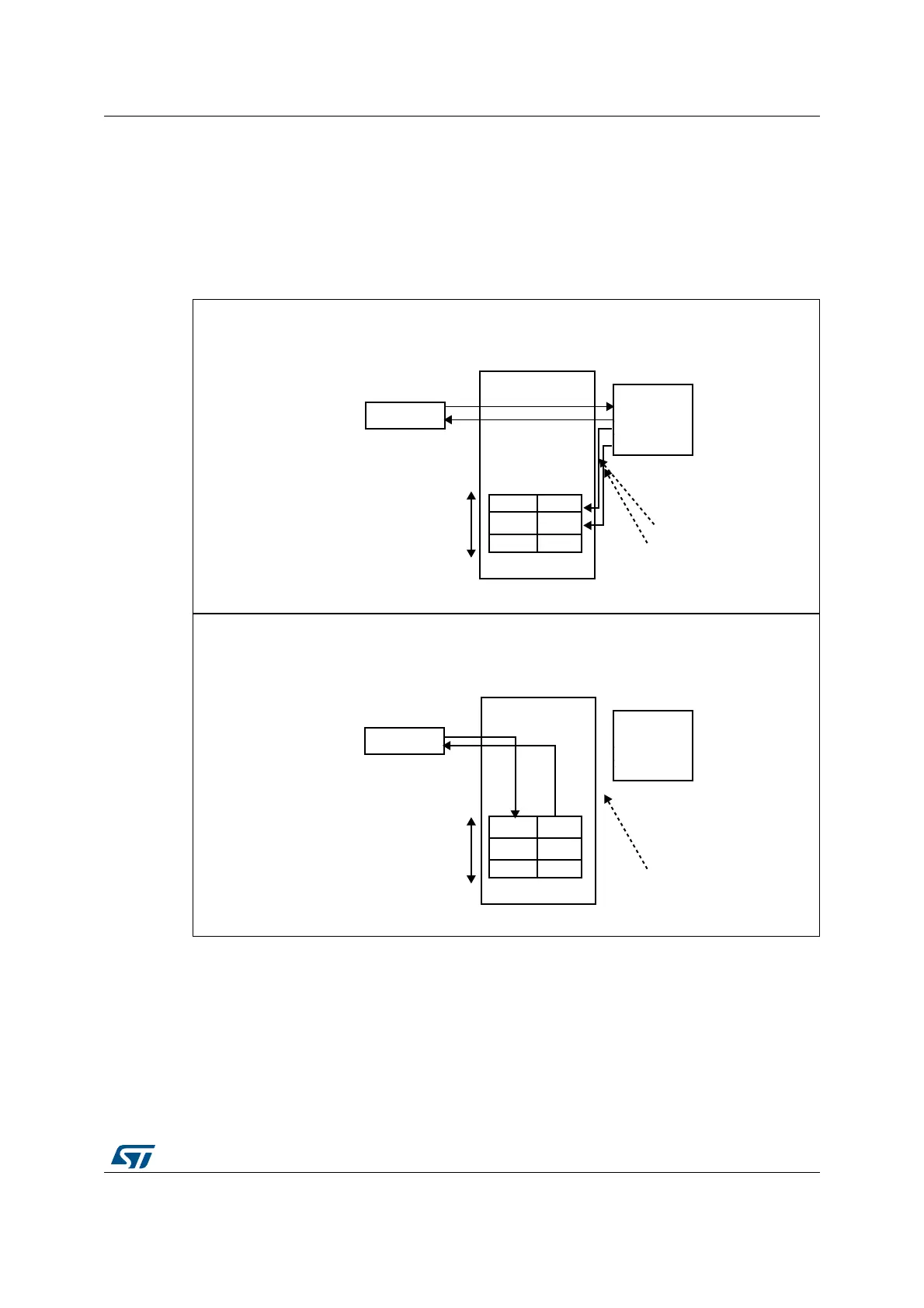

Figure 480. Logic diagram of Read access with RBURST bit set (CAS=2, RPIPE=0)

During a write access or a Precharge command, the read FIFO is flushed and ready to be

filled with new data.

After the first read request, if the current access was not performed to a row boundary, the

SDRAM controller anticipates the next read access during the CAS latency period and the

RPIPE delay (if configured). This is done by incrementing the memory address. The

following condition must be met:

• RBURST control bit should be set to ‘1’ in the FMC_SDCR1 register.

MS30445V1

AHB Master

@0x04

@0x08

Data 2

Data 3

...

...

SDRAM

Device

(CAS = 2)

read request@0x00

Data 1

6 lines FIFO

Add. Tag read FIFO

Data stored in FIFO

in advance during

the CAS latency period

Address matches with

one of the address tags

FMC SDRAM Controller

2nd Read access : Requested data was previously stored in the FIFO

1st Read access: Requested data is not in the FIFO

AHB Master

@0x04

@0x08

Data 2

Data 3

...

...

SDRAM

Device

(CAS = 2)

read request@0x04

Data 2

6 lines FIFO

Data read from FIFO

FMC SDRAM Controller

Add. Tag read FIFO

Loading...

Loading...