Serial peripheral interface (SPI) RM0090

898/1749 RM0090 Rev 18

CRC error

This flag is used to verify the validity of the value received when the CRCEN bit in the

SPI_CR1 register is set. The CRCERR flag in the SPI_SR register is set if the value

received in the shift register does not match the receiver SPI_RXCRCR value.

TI mode frame format error

A TI mode frame format error is detected when an NSS pulse occurs during an ongoing

communication when the SPI is acting in slave mode and configured to conform to the TI

mode protocol. When this error occurs, the FRE flag is set in the SPI_SR register. The SPI

is not disabled when an error occurs, the NSS pulse is ignored, and the SPI waits for the

next NSS pulse before starting a new transfer. The data may be corrupted since the error

detection may result in the lost of two data bytes.

The FRE flag is cleared when SPI_SR register is read. If the bit ERRIE is set, an interrupt is

generated on the NSS error detection. In this case, the SPI should be disabled because

data consistency is no more guaranteed and communications should be reinitiated by the

master when the slave SPI is re-enabled.

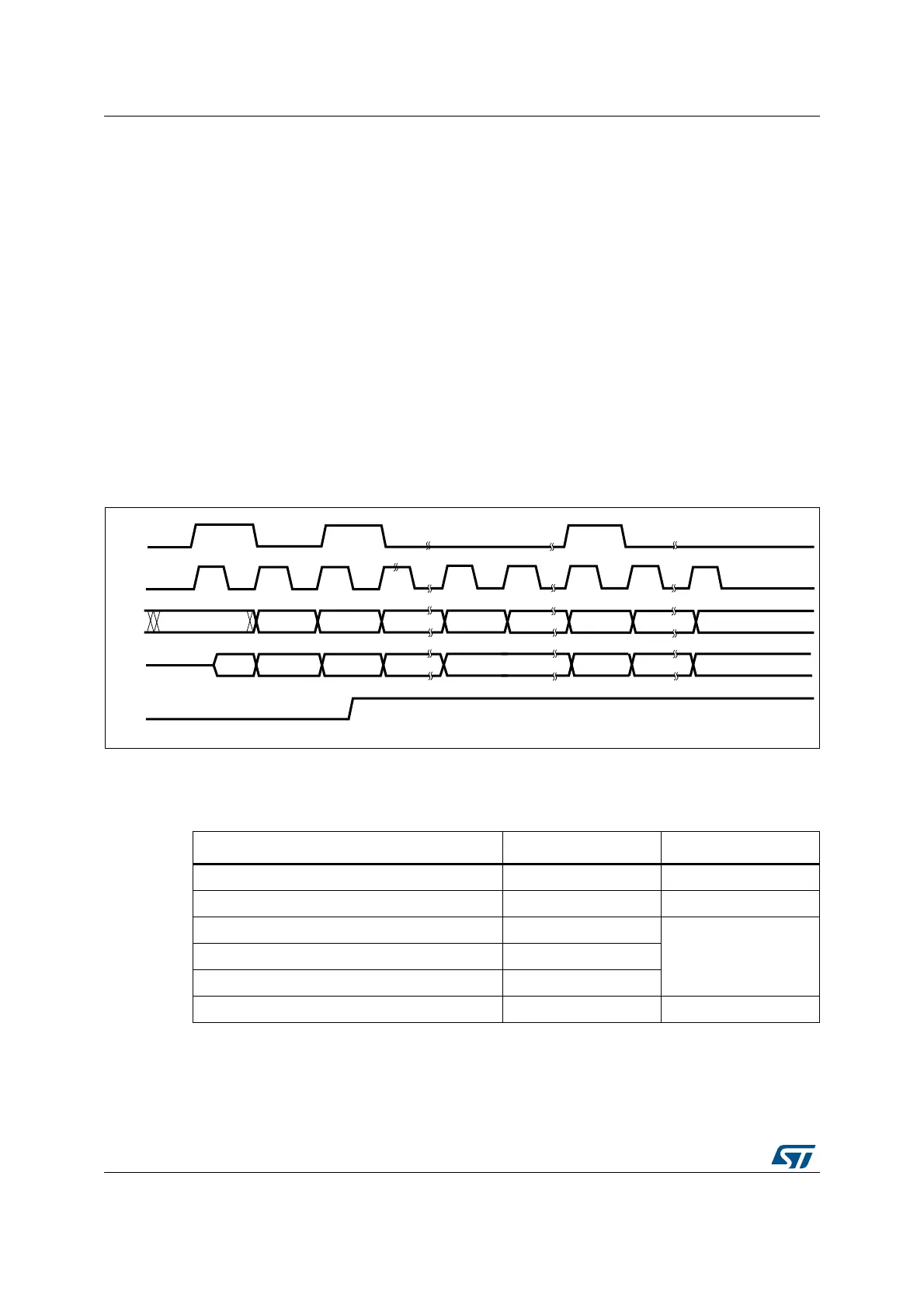

Figure 261. TI mode frame format error detection

28.3.11 SPI interrupts

ai18438

MSBIN

MOSI

input

NSS

output

SCK

output

trigger sampling trigger sampling trigger sampling

DONTCARE

MISO

output

1 or 0 MSBOUT

LSBOUT

MSBIN LSBIN

MSBOUT LSBOUT

trigger sampling trigger sampling trigger sampling trigger sampling

LSBIN DONTCARE

TIFRFE

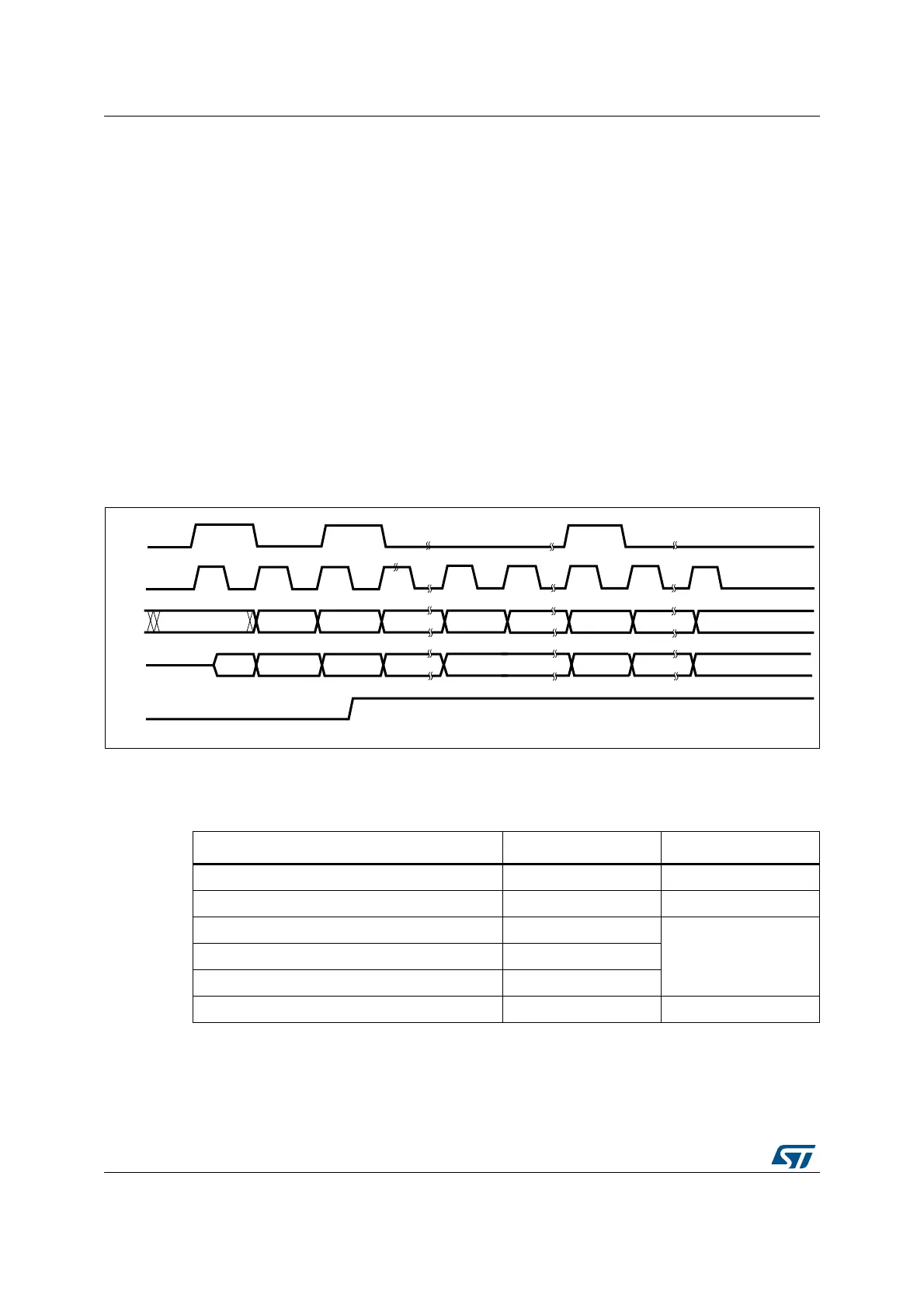

Table 126. SPI interrupt requests

Interrupt event Event flag Enable Control bit

Transmit buffer empty flag TXE TXEIE

Receive buffer not empty flag RXNE RXNEIE

Master Mode fault event MODF

ERRIEOverrun error OVR

CRC error flag CRCERR

TI frame format error

FRE

ERRIE

Loading...

Loading...