Advanced-control timers (TIM1 and TIM8) RM0090

542/1749 RM0090 Rev 18

compare value in TIMx_CCRx is greater than the auto-reload value (in TIMx_ARR)

then OCxREF is held at ‘1’. If the compare value is 0 then OCxRef is held at ‘0’.

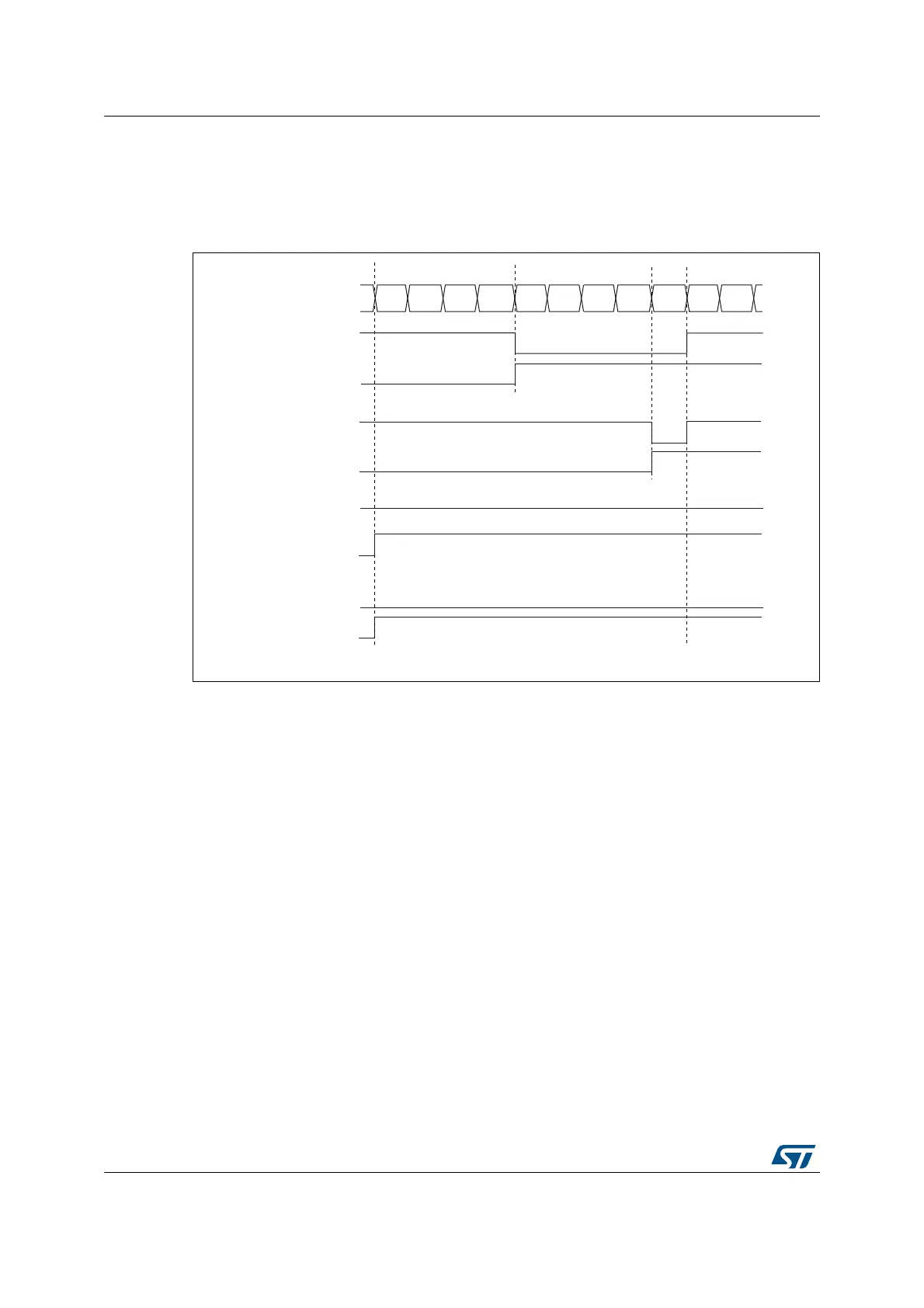

Figure 118 shows some edge-aligned PWM waveforms in an example where

TIMx_ARR=8.

Figure 118. Edge-aligned PWM waveforms (ARR=8)

• Downcounting configuration

Downcounting is active when DIR bit in TIMx_CR1 register is high. Refer to

Downcounting mode

In PWM mode 1, the reference signal OCxRef is low as long as

TIMx_CNT > TIMx_CCRx else it becomes high. If the compare value in TIMx_CCRx is

greater than the auto-reload value in TIMx_ARR, then OCxREF is held at ‘1’. 0% PWM

is not possible in this mode.

PWM center-aligned mode

Center-aligned mode is active when the CMS bits in TIMx_CR1 register are different from

‘00’ (all the remaining configurations having the same effect on the OCxRef/OCx signals).

The compare flag is set when the counter counts up, when it counts down or both when it

counts up and down depending on the CMS bits configuration. The direction bit (DIR) in the

MS31093V1

Counter register

‘1’

0

12 3456 7801

OCXREF

CCxIF

OCXREF

CCxIF

OCXREF

CCxIF

OCXREF

CCxIF

CCRx=4

CCRx=8

CCRx>8

CCRx=0

‘0’

Loading...

Loading...