RM0090 Rev 18 709/1749

RM0090 Independent watchdog (IWDG)

712

different value will break the sequence and register access will be protected again. This

implies that it is the case of the reload operation (writing 0xAAAA).

A status register is available to indicate that an update of the prescaler or the down-counter

reload value is on going.

21.3.3 Debug mode

When the microcontroller enters debug mode (Cortex

®

-M4 with FPU core halted), the IWDG

counter either continues to work normally or stops, depending on DBG_IWDG_STOP

configuration bit in DBG module. For more details, refer to Section 38.16.2: Debug support

for timers, watchdog, bxCAN and I

2

C.

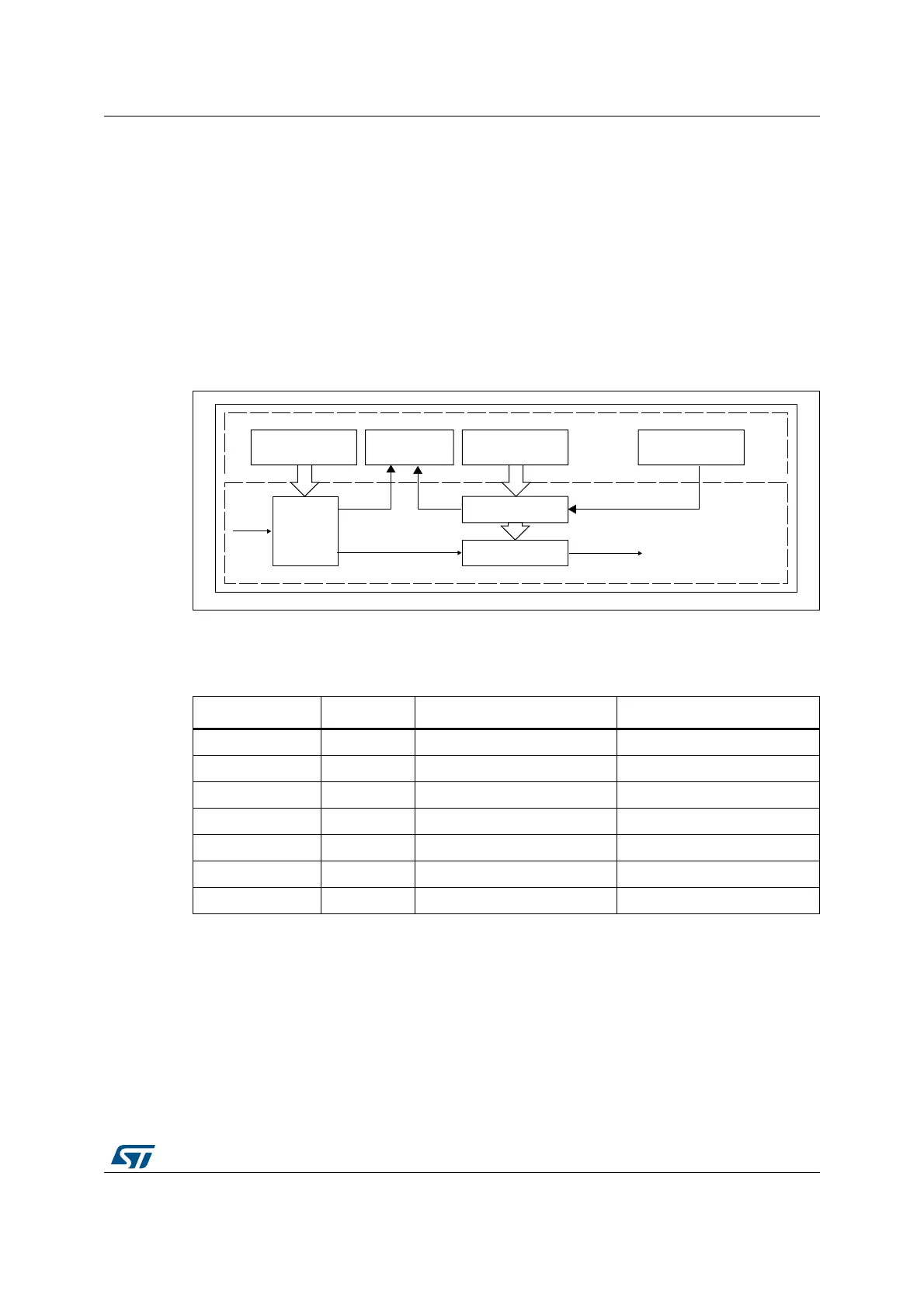

Figure 213. Independent watchdog block diagram

Note: The watchdog function is implemented in the V

DD

voltage domain, still functional in Stop and

Standby modes.

IWDG reset

prescaler

IWDG_PR

Prescaler register

IWDG_RLR

Reload register

8-bit

LSI

(40 kHz)

IWDG_KR

Key register

CORE

VDD voltage domain

IWDG_SR

Status register

MS19944V2

12-bit reload value

12-bit downcounter

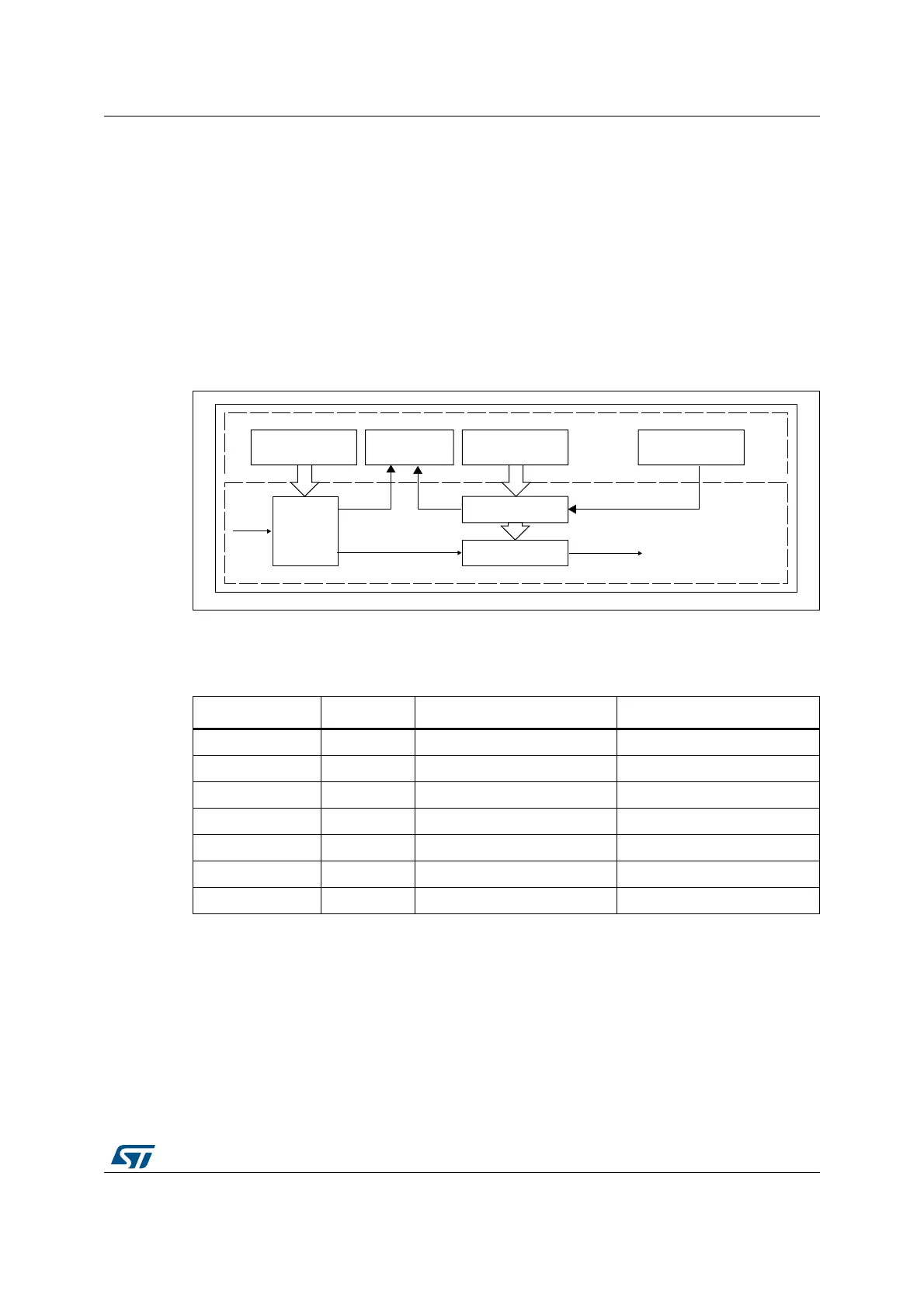

Table 107. Min/max IWDG timeout period (in ms) at 32 kHz (LSI)

(1)

1. These timings are given for a 32 kHz clock but the microcontroller internal RC frequency can vary. Refer to

the LSI oscillator characteristics table in the device datasheet for maximum and minimum values.

Prescaler divider PR[2:0] bits Min timeout RL[11:0]= 0x000 Max timeout RL[11:0]= 0xFFF

/4 0 0.125 512

/8 1 0.25 1024

/16 2 0.5 2048

/32 3 1 4096

/64 4 2 8192

/128 5 4 16384

/256 6 8 32768

Loading...

Loading...