RM0090 Rev 18 1339/1749

RM0090 USB on-the-go full-speed (OTG_FS)

1380

The application must ignore all packet statuses other than IN data packet (bx0010).

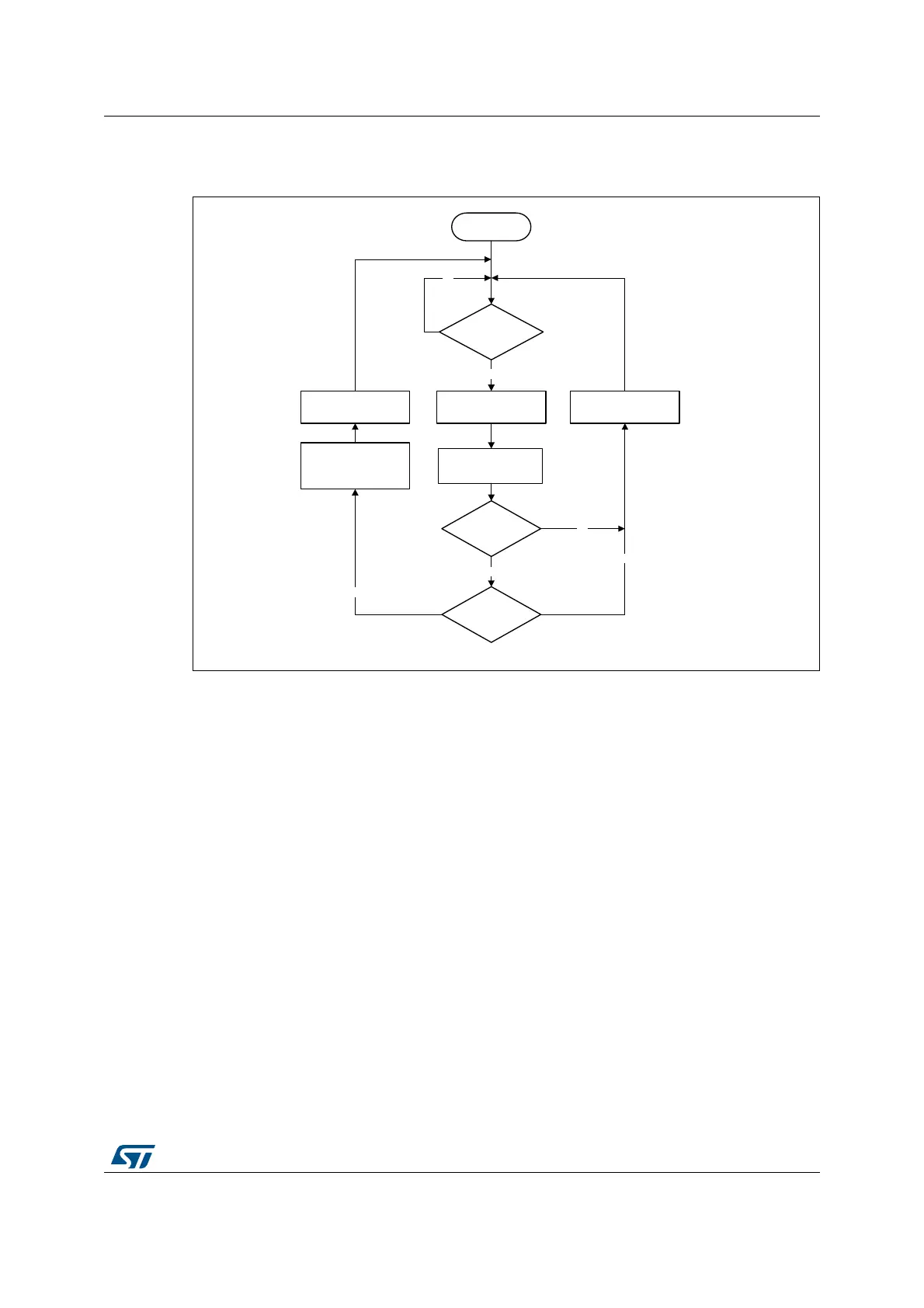

Figure 397. Receive FIFO read task

• Bulk and control OUT/SETUP transactions

A typical bulk or control OUT/SETUP pipelined transaction-level operation is shown in

Figure 398. See channel 1 (ch_1). Two bulk OUT packets are transmitted. A control

SETUP transaction operates in the same way but has only one packet. The

assumptions are:

– The application is attempting to send two maximum-packet-size packets (transfer

size = 1, 024 bytes).

– The non-periodic transmit FIFO can hold two packets (128 bytes for FS).

– The non-periodic request queue depth = 4.

• Normal bulk and control OUT/SETUP operations

The sequence of operations in (channel 1) is as follows:

a) Initialize channel 1

b) Write the first packet for channel 1

c) Along with the last word write, the core writes an entry to the non-periodic request

queue

d) As soon as the non-periodic queue becomes non-empty, the core attempts to

send an OUT token in the current frame

e) Write the second (last) packet for channel 1

f) The core generates the XFRC interrupt as soon as the last transaction is

completed successfully

RXFLVL

interrupt ?

Read the received

packet from the

Receive FIFO

Read

OTG_FS_GRXSTSP

PKTSTS

0b0010?

Yes

Yes

Unmask RXFLVL

interrupt

BCNT > 0?

No

Mask RXFLVL

interrupt

Yes

Unmask RXFLVL

interrupt

No

No

Start

ai1567

Loading...

Loading...