General-purpose I/Os (GPIO) RM0090

282/1749 RM0090 Rev 18

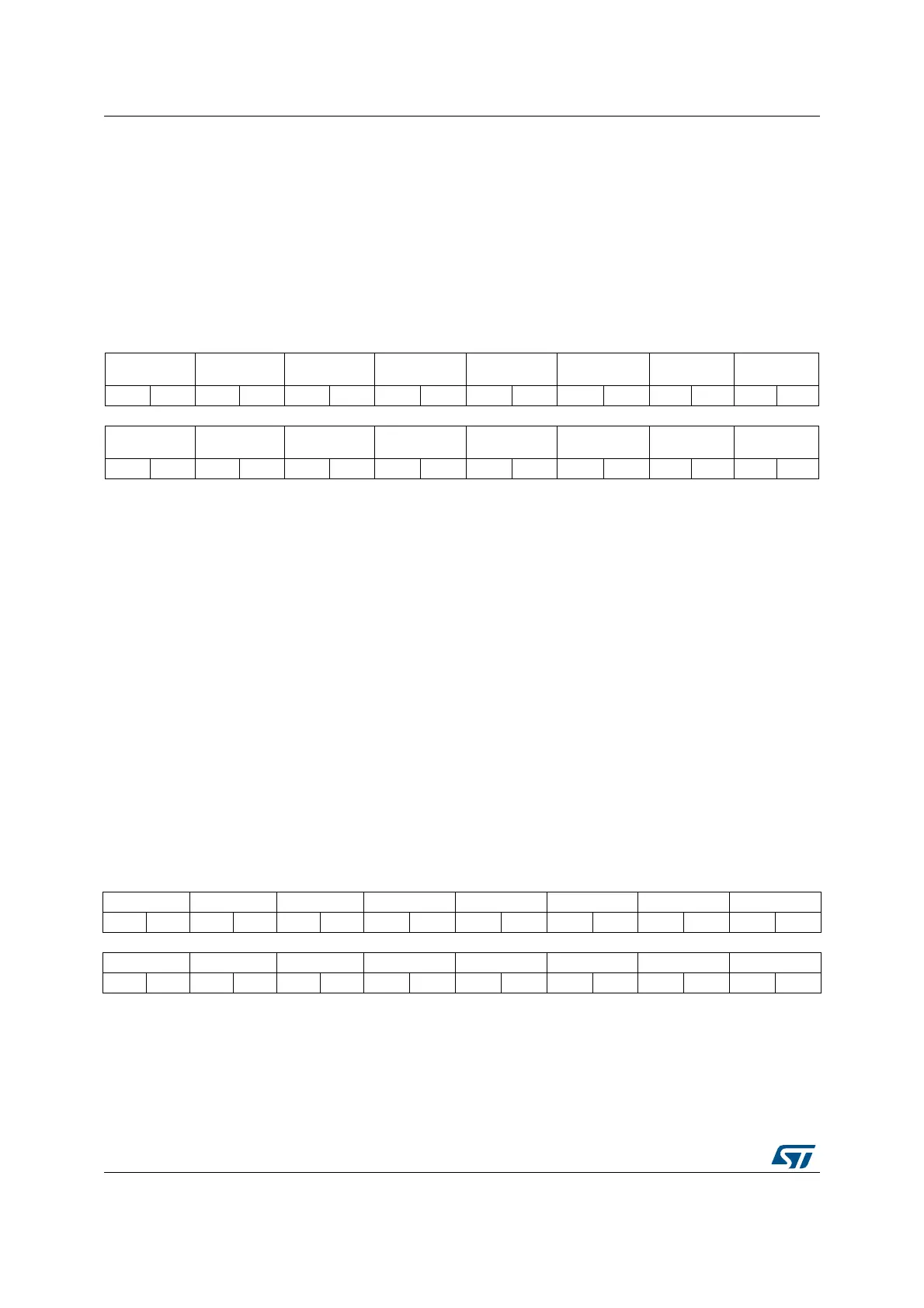

8.4.3 GPIO port output speed register (GPIOx_OSPEEDR)

(x = A..I/J/K)

Address offset: 0x08

Reset values:

• 0x0C00 0000 for port A

• 0x0000 00C0 for port B

• 0x0000 0000 for other ports

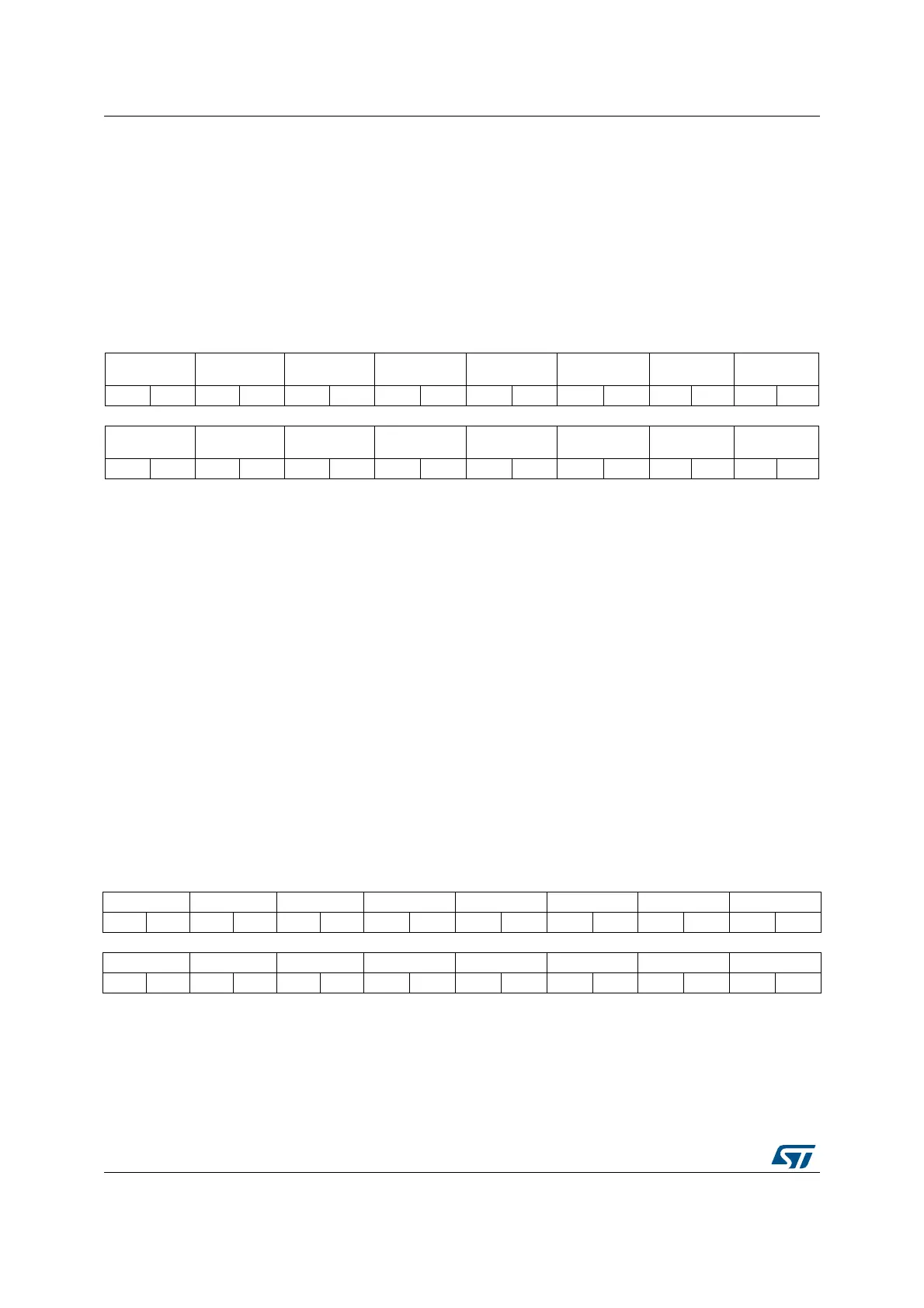

8.4.4 GPIO port pull-up/pull-down register (GPIOx_PUPDR)

(x = A..I/J/K)

Address offset: 0x0C

Reset values:

• 0x6400 0000 for port A

• 0x0000 0100 for port B

• 0x0000 0000 for other ports

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

OSPEEDR15

[1:0]

OSPEEDR14

[1:0]

OSPEEDR13

[1:0]

OSPEEDR12

[1:0]

OSPEEDR11

[1:0]

OSPEEDR10

[1:0]

OSPEEDR9

[1:0]

OSPEEDR8

[1:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OSPEEDR7[1:0] OSPEEDR6[1:0] OSPEEDR5[1:0] OSPEEDR4[1:0] OSPEEDR3[1:0] OSPEEDR2[1:0]

OSPEEDR1

[1:0]

OSPEEDR0

1:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 2y:2y+1 OSPEEDRy[1:0]: Port x configuration bits (y = 0..15)

These bits are written by software to configure the I/O output speed.

00: Low speed

01: Medium speed

10: High speed

11: Very high speed

Note: Refer to the product datasheets for the values of OSPEEDRy bits versus V

DD

range and external load.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PUPDR15[1:0] PUPDR14[1:0] PUPDR13[1:0] PUPDR12[1:0] PUPDR11[1:0] PUPDR10[1:0] PUPDR9[1:0] PUPDR8[1:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

PUPDR7[1:0] PUPDR6[1:0] PUPDR5[1:0] PUPDR4[1:0] PUPDR3[1:0] PUPDR2[1:0] PUPDR1[1:0] PUPDR0[1:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...