Memory and bus architecture RM0090

62/1749 RM0090 Rev 18

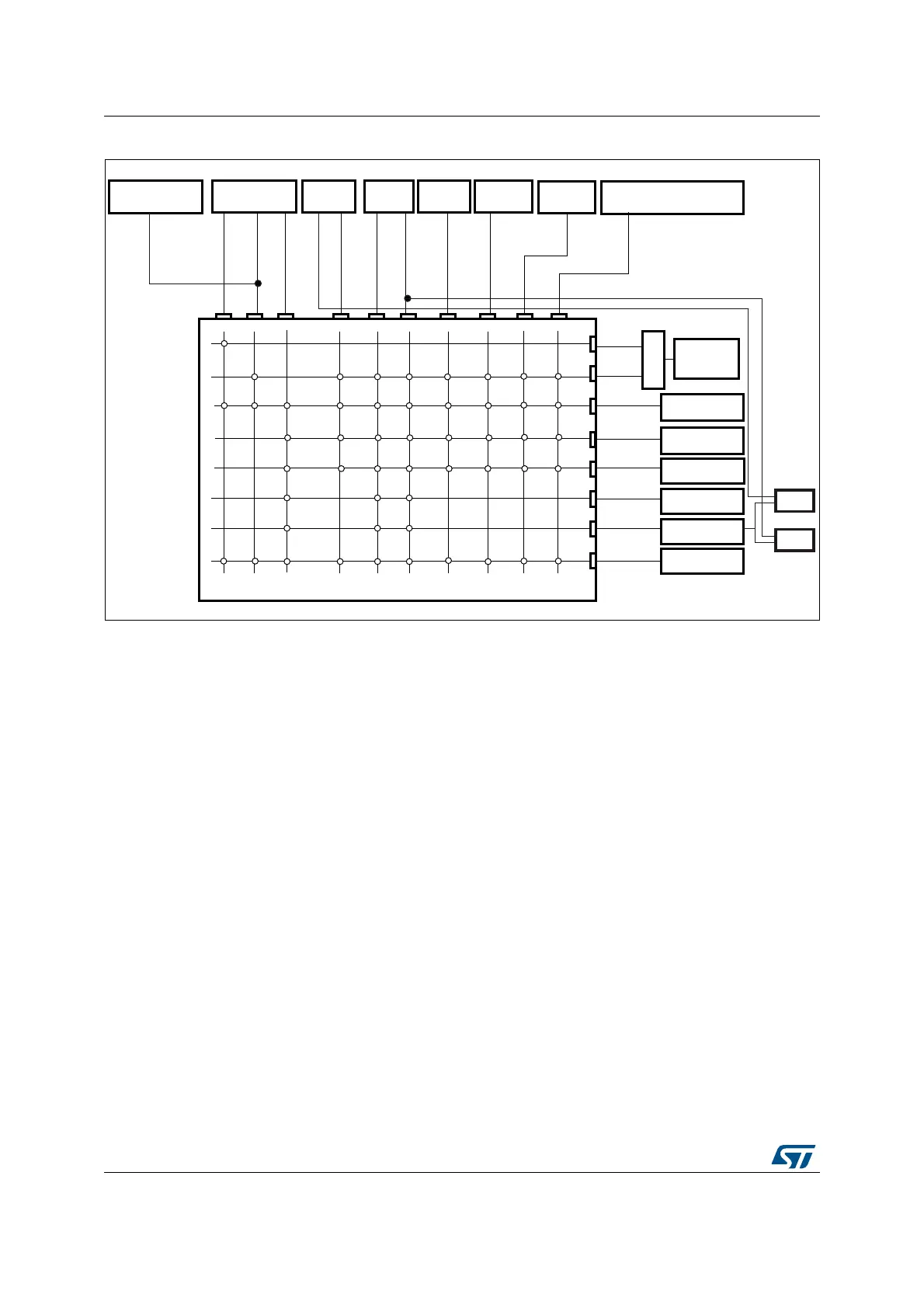

Figure 2. System architecture for STM32F42xxx and STM32F43xxx devices

2.1.1 I-bus

This bus connects the Instruction bus of the Cortex

®

-M4 with FPU core to the BusMatrix.

This bus is used by the core to fetch instructions. The target of this bus is a memory

containing code (internal Flash memory/SRAM or external memories through the

FSMC/FMC).

2.1.2 D-bus

This bus connects the databus of the Cortex

®

-M4 with FPU to the 64-Kbyte CCM data RAM

to the BusMatrix. This bus is used by the core for literal load and debug access. The target

of this bus is a memory containing code or data (internal Flash memory or external

memories through the FSMC/FMC).

2.1.3 S-bus

This bus connects the system bus of the Cortex

®

-M4 with FPU core to a BusMatrix. This

bus is used to access data located in a peripheral or in SRAM. Instructions may also be

fetched on this bus (less efficient than ICode). The targets of this bus are the internal

SRAM1, SRAM2 and SRAM3, the AHB1 peripherals including the APB peripherals, the

AHB2 peripherals and the external memories through the FSMC/FMC.

ARM

Cortex-M4

GP

DMA1

GP

DMA2

MAC

Ethernet

USB OTG

HS

Bus matrix-S

ICODE

DCODE

ACCEL

Flash

memory

SRAM1

112 Kbyte

SRAM2

16 Kbyte

AHB2

peripherals

AHB1

peripherals

FMC external

MemCtl

I-bus

D-bus

S-bus

DMA_PI

DMA_MEM1

DMA_MEM2

DMA_P2

ETHERNET_M

USB_HS_M

MS30421V6

CCM data RAM

64-Kbyte

APB1

APB2

SRAM3

64 Kbyte

LCD-TFT

Chrom ART Accelerator

(DMA2D)

LCD-TFT_M

DMA2D

Loading...

Loading...