Serial audio interface (SAI) RM0090

946/1749 RM0090 Rev 18

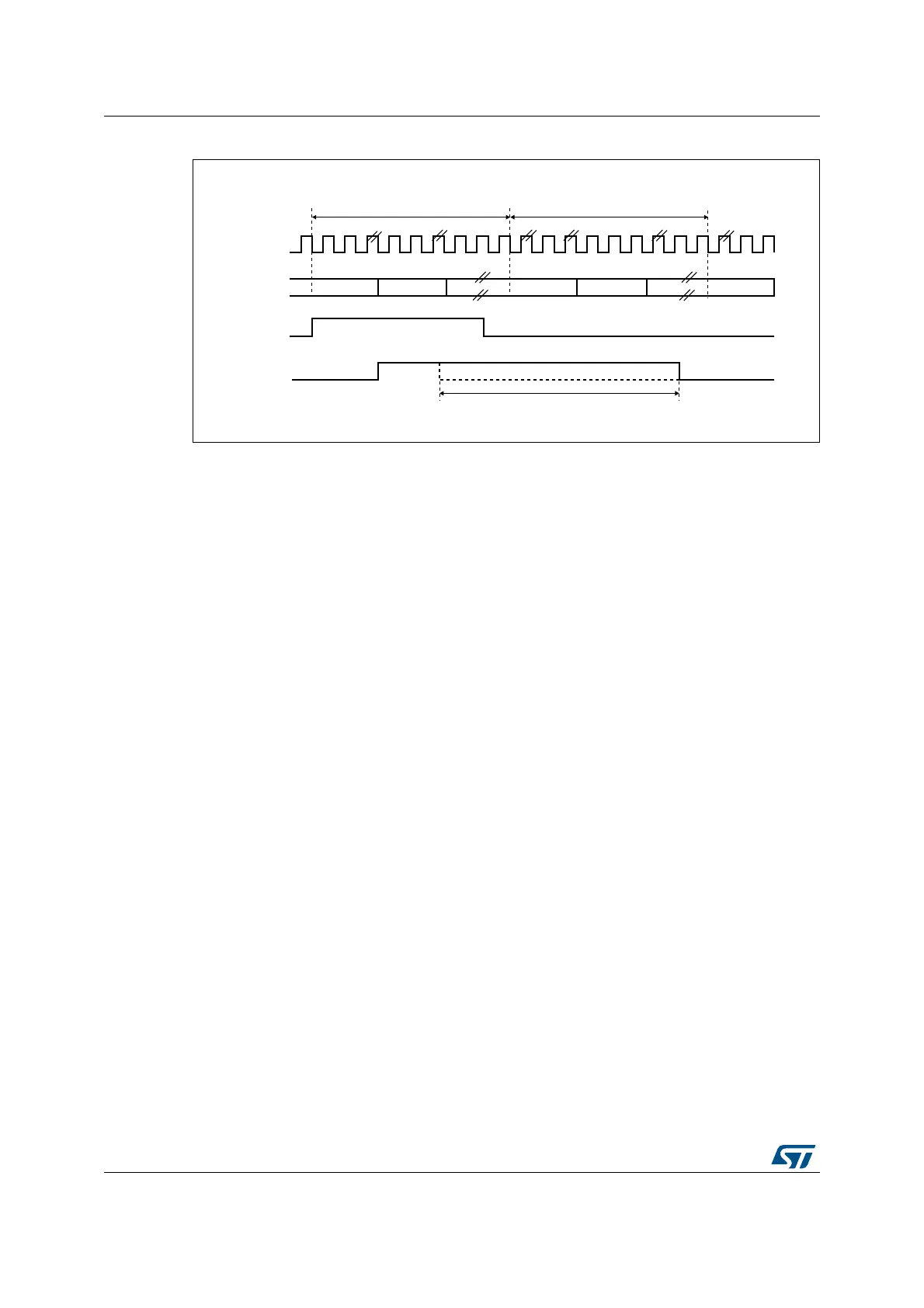

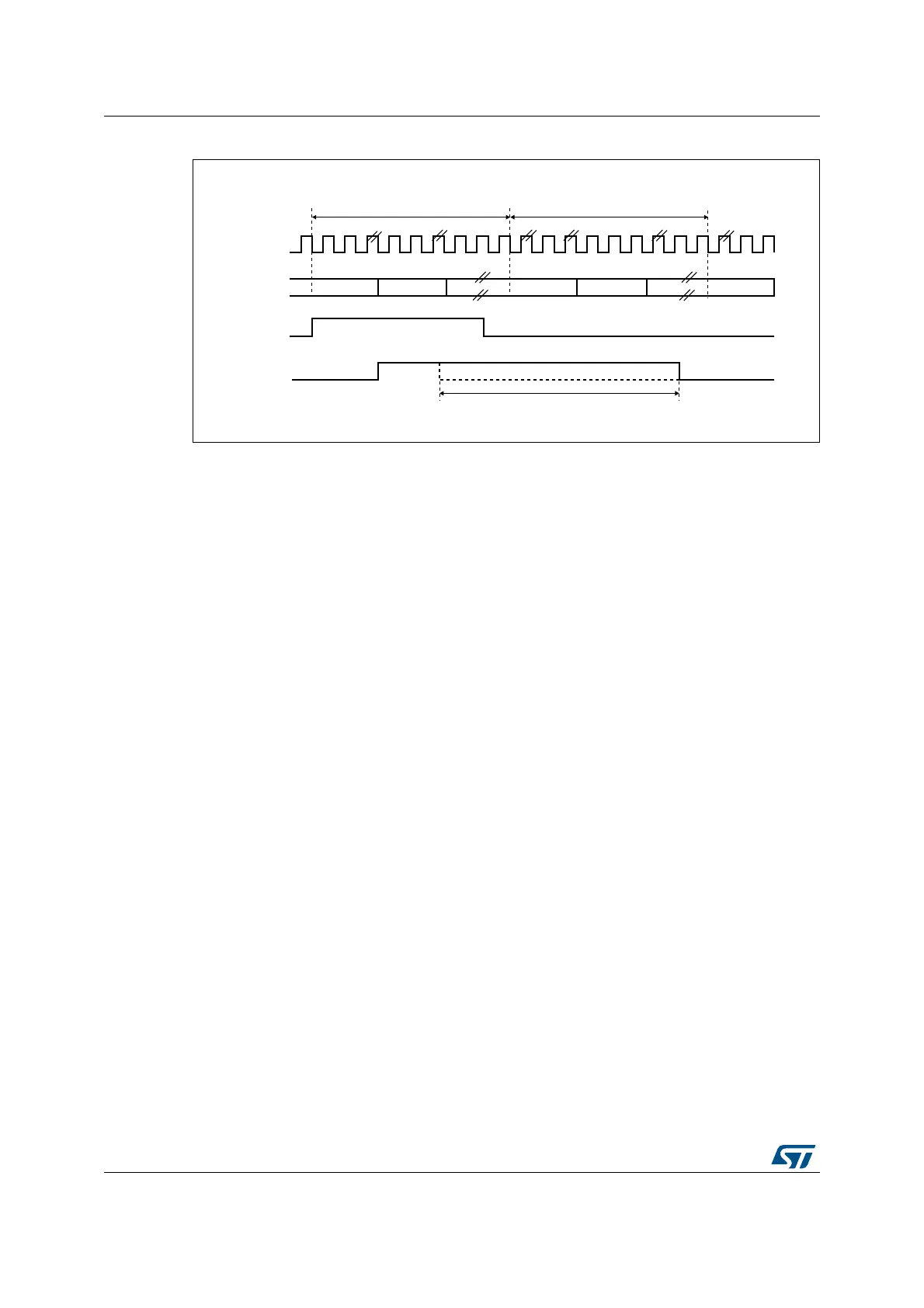

Figure 295. FIFO underrun event

29.13.2 Anticipated frame synchronisation detection (AFSDET)

This flag AFSDET is used only in Slave mode. In master mode, it is never asserted. It

informs about the detection of a frame synchronisation (FS) earlier than expected since the

frame length, the frame polarity, the frame offset are defined and known.

Early detection sets flag AFSDET in the SAI_xSR register.

This detection has no effect on the current audio frame which is not sensitive to the

anticipated FS. This means that “parasitic” events on signal FS are flagged without any

perturbation of the current audio frame.

If bit AFSDETIE is set in the SAI_xIM register, an interrupt is generated. To clear the flag

AFSDET, bit CAFSDET in the SAI_xCLRFR register has to be set.

To resynchronize with the master after Anticipated frame detection error, four steps should

be respected:

1. SAI block should be disabled by resetting SAIEN bit in SAI_xCR1 register, to be sure

that the SAI is disabled SAIEN bit is should be equal to 0 (reading back this bit).

2. FIFO should be flushed via FFLUS bit in SAI_xCR2 register.

3. Re-enabling the SAI peripheral (SAIEN bit set to 1) then the SAI.

4. SAI block will wait for the assertion on FS to restart the synchronization with master.

Note: This flag is not asserted in AC’97 since the SAI audio block acts as a link controller and

generates the FS signal even when declared as slave.

29.13.3 Late frame synchronization detection

Flag LFSDET in the SAI_xSR register can be set only when the SAI audio block is defined

as slave. The frame length, the frame polarity and the frame offset configuration are known

in register SAI_xFRCR.

If the external master does not send the FS signal at the expecting time (generating the

signal too late), the flag LFSDET in the SAI_xSR register will be set and an interrupt is

generated if bit LFSDETIE in the SAI_xIM register is set.

The flag is cleared when bit CLFSDET is set in the SAI_xCLRFR register.

MS192347V2

sck

data

Slot 0 ON MUTE

Slot size = data size

SD (output)

Example: FIFO underrun on Slot 1

Audio frame Audio frame

MUTE Slot 1 ON ... ON Slot 0 ON

OVRUND=1

MUTE

FIFO empty

OVRUND

Loading...

Loading...