DMA controller (DMA) RM0090

308/1749 RM0090 Rev 18

10.3.4 Arbiter

An arbiter manages the 8 DMA stream requests based on their priority for each of the two

AHB master ports (memory and peripheral ports) and launches the peripheral/memory

access sequences.

Priorities are managed in two stages:

• Software: each stream priority can be configured in the DMA_SxCR register. There are

four levels:

– Very high priority

– High priority

– Medium priority

– Low priority

• Hardware: If two requests have the same software priority level, the stream with the

lower number takes priority over the stream with the higher number. For example,

Stream 2 takes priority over Stream 4.

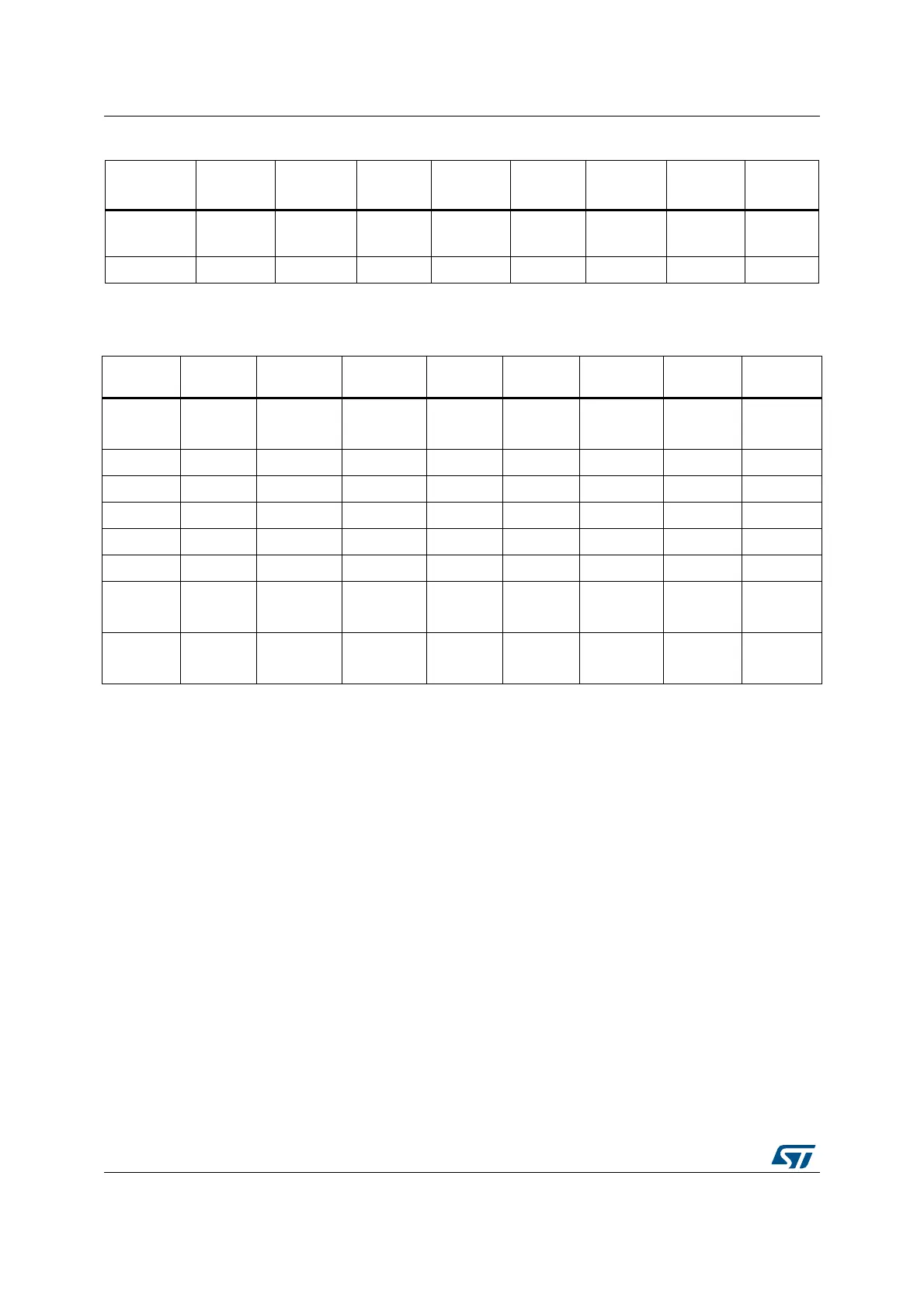

Channel 6

TIM5_CH3

TIM5_UP

TIM5_CH4

TIM5_TRIG

TIM5_CH1

TIM5_CH4

TIM5_TRIG

TIM5_CH2 - TIM5_UP -

Channel 7 - TIM6_UP I2C2_RX I2C2_RX USART3_TX DAC1 DAC2 I2C2_TX

1. These requests are available on STM32F42xxx and STM32F43xxx only.

Table 42. DMA1 request mapping (continued)

Peripheral

requests

Stream 0 Stream 1 Stream 2 Stream 3 Stream 4 Stream 5 Stream 6 Stream 7

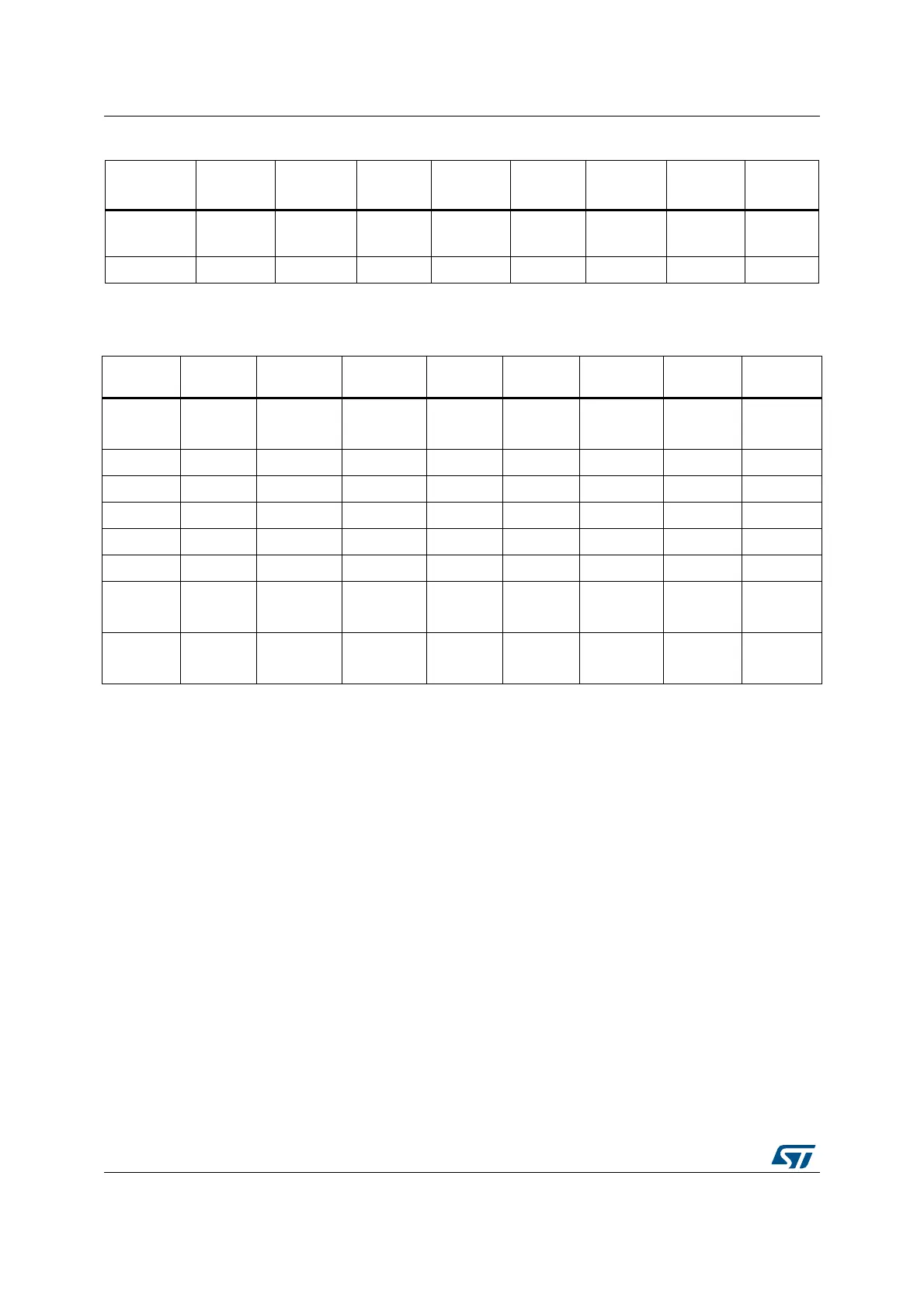

Table 43. DMA2 request mapping

Peripheral

requests

Stream 0 Stream 1 Stream 2 Stream 3 Stream 4 Stream 5 Stream 6 Stream 7

Channel 0 ADC1 SAI1_A

(1)

TIM8_CH1

TIM8_CH2

TIM8_CH3

SAI1_A

(1)

ADC1 SAI1_B

(1)

TIM1_CH1

TIM1_CH2

TIM1_CH3

-

Channel 1

-

DCMI ADC2 ADC2 SAI1_B

(1)

SPI6_TX

(1)

SPI6_RX

(1)

DCMI

Channel 2 ADC3 ADC3

-

SPI5_RX

(1)

SPI5_TX

(1)

CRYP_OUT CRYP_IN HASH_IN

Channel 3 SPI1_RX

-

SPI1_RX SPI1_TX

-

SPI1_TX

--

Channel 4 SPI4_RX

(1)

SPI4_TX

(1)

USART1_RX SDIO

-

USART1_RX SDIO USART1_TX

Channel 5

-

USART6_RX USART6_RX SPI4_RX

(1)

SPI4_TX

(1)

-

USART6_TX USART6_TX

Channel 6 TIM1_TRIG TIM1_CH1 TIM1_CH2 TIM1_CH1

TIM1_CH4

TIM1_TRIG

TIM1_COM

TIM1_UP TIM1_CH3

-

Channel 7

-

TIM8_UP TIM8_CH1 TIM8_CH2 TIM8_CH3 SPI5_RX

(1)

SPI5_TX

(1)

TIM8_CH4

TIM8_TRIG

TIM8_COM

1. These requests are available on STM32F42xxx and STM32F43xxx.

Loading...

Loading...