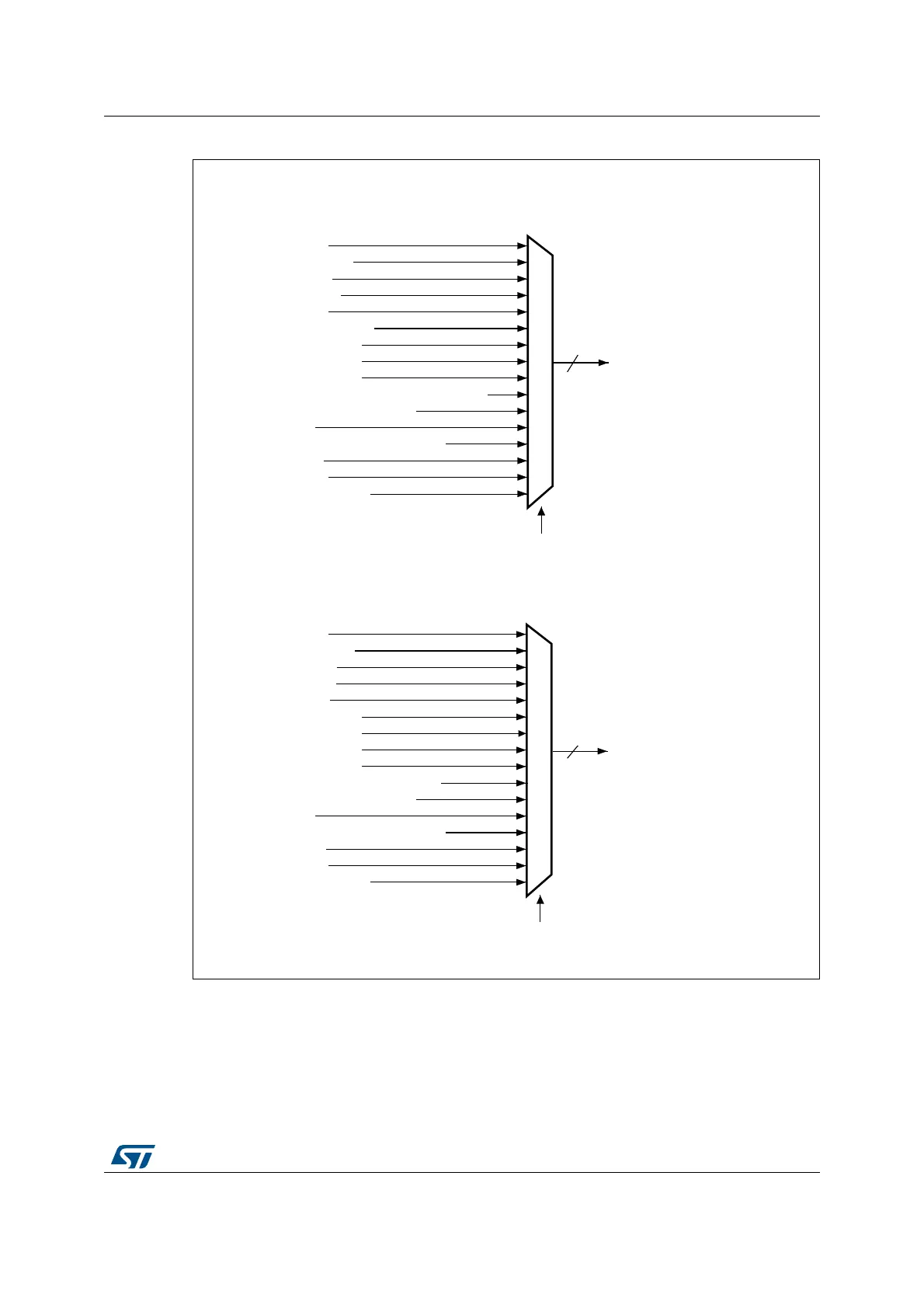

Figure 27. Selecting an alternate function on STM32F42xxx and STM32F43xxx

1. Configured in FS.

MS60208V1

For pins 0 to 7, the GPIOx_AFRL[31:0] register selects the dedicated alternate function

AF0 (system)

AF1 (TIM1/TIM2)

AF2 (TIM3..5)

AF3 (TIM8..11)

AF4 (I2C1..3)

AF5 (SPI1/2/3/4/5/6)

AF6 (SPI2/3/SAI1)

AF7 (USART1..3)

AF8 (USART4..8)

AF9 (CAN1/CAN2, LTDC, TIM12..14)

AF10 (OTG_FS, OTG_HS)

AF11 (ETH)

AF12 (FMC, SDIO, OTG_HS

(1)

)

AF13 (DCMI)

AF14 (LTDC)

AF15 (EVENTOUT)

Pin x (x = 0..7)

AFRL[31:0]

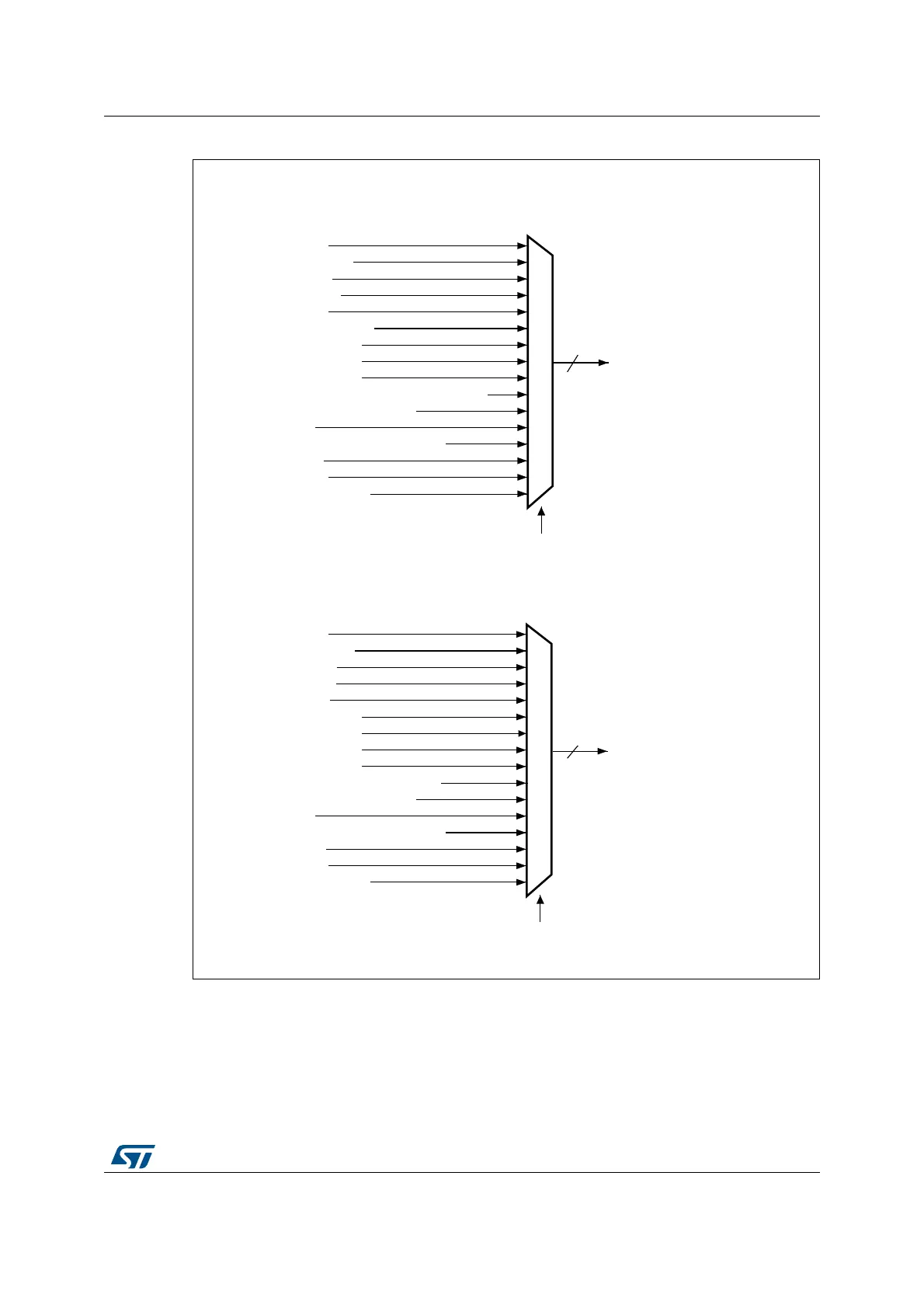

For pins 8 to 15, the GPIOx_AFRH[31:0] register selects the dedicated alternate function

AF0 (system)

AF1 (TIM1/TIM2)

AF2 (TIM3..5)

AF3 (TIM8..11)

AF4 (I2C1..3)

AF5 (SPI1/2/4/5/6)

AF6 (SPI2/3/SAI1)

AF7 (USART1..3)

AF8 (USART4..8)

AF9 (CAN1/CAN2, TIM12..14)

AF10 (OTG_FS, OTG_HS)

AF11 (ETH)

AF12 (FMC, SDIO, OTG_HS

(1)

)

AF13 (DCMI)

AF14 (LTDC)

AF15 (EVENTOUT)

Pin x (x = 8..15)

AFRH[31:0]

1

1

Loading...

Loading...