Serial audio interface (SAI) RM0090

930/1749 RM0090 Rev 18

29.5 SAI synchronization mode

Internal synchronization

An audio block can be declared synchronous with the second audio block. In this case, the

bit clock and the frame synchronization signals are shared to reduce the number of external

pins used for the communication. The audio block declared as synchronous with the other

one will see its own SCK_x, FS_x, and MCLK_x pins released to bring them back as GPIOs.

The one declared asynchronous is the one for which the I/O pins FS_x and SCK_x ad

MCLK_x (if the audio block is considered as master) are considered.

Typically, the audio block synchronous mode may be used to configure the SAI in full duplex

mode. One of the two audio blocks can be configured as master and the other as slave, or

both can be slaves; with one block declared as asynchronous (respective bit SYNCEN[1:0]

= 00 in SAI_xCR1) and the other one declared as synchronous with the other audio block

(respective bit SYNCEN[1:0] = 01 in the SAI_xCR1).

Note: APB frequency PCLK must be greater or equal to twice the bit rate clock frequency (due to

internal resynchronization stages).

29.6 Audio data size

The audio frame can target different data sizes by configuring bit DS[2:0] in the SAI_xCR1

register. The data sizes may be 8-, 10-, 16-, 20-, 24- or 32-bit. During the transfer, either the

MSB or the LSB of the data are sent first, depending on the configuration of bit LSBFIRST in

the SAI_xCR1 register.

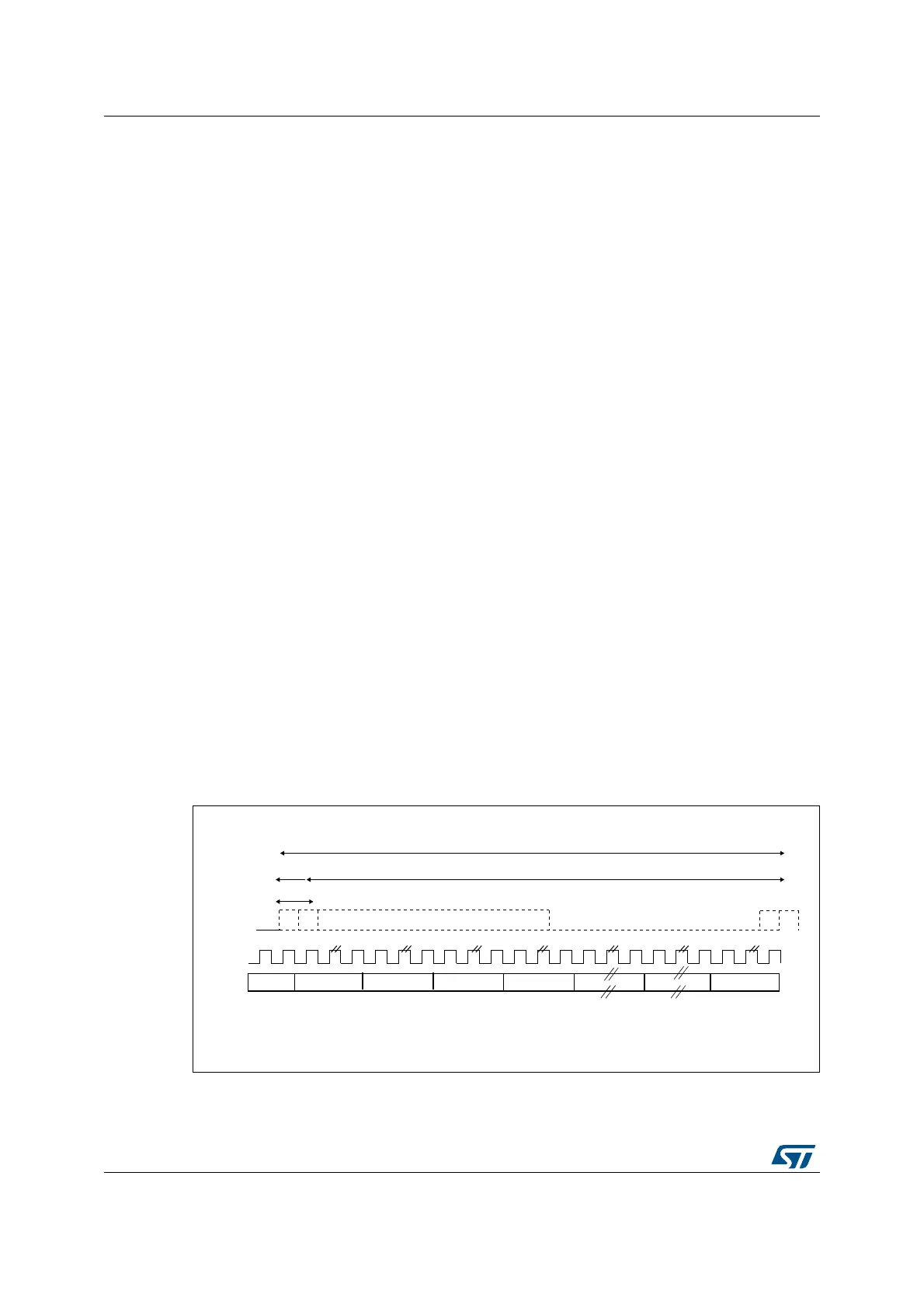

29.7 Frame synchronization

The FS signal acts as the Frame synchronization signal in the audio frame (start of frame).

The shape of this signal is completely configurable in order to target the different audio

protocols with their own specificities concerning this Frame synchronization behavior. This

configurability is done using register SAI_xFRCR. Figure 284 gives a view of this flexibility.

Figure 284. Audio frame

Slot 0

Fs

sck

sd

Fs offset

Fs length = < 256 bits

Fs active length = < 128 bits

MS30037V1

Slot 1 Slot 2 Slot 3 Slot n

…

…

Loading...

Loading...