RM0090 Rev 18 1457/1749

RM0090 USB on-the-go high-speed (OTG_HS)

1543

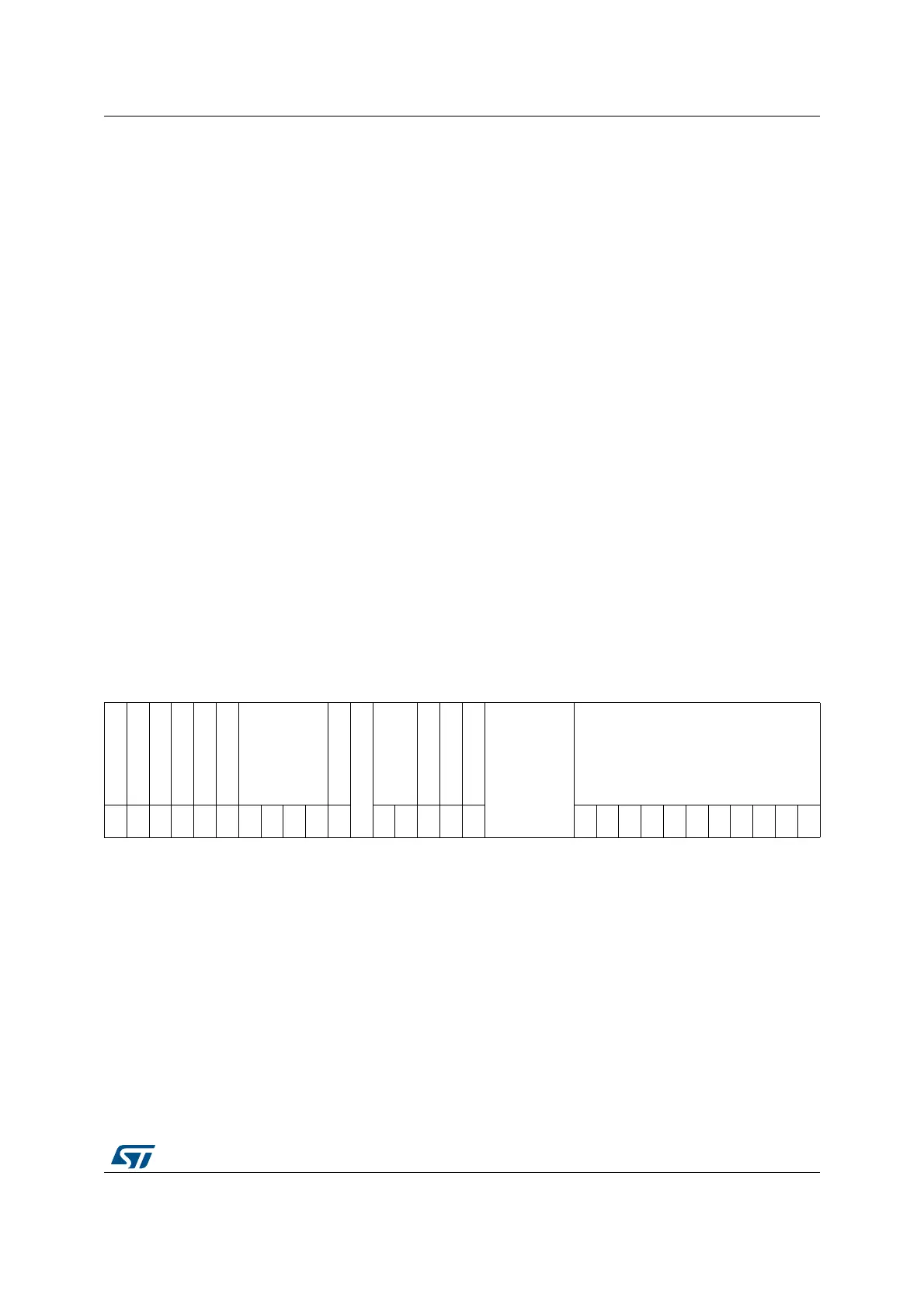

OTG device endpoint-x control register (OTG_HS_DIEPCTLx) (x = 0..5, where

x = Endpoint_number)

Address offset: 0x900 + 0x20 * x

Reset value: 0x0000 0000

The application uses this register to control the behavior of each logical endpoint other than

endpoint 0.

Bit 9 BIM: BNA interrupt mask

0: Masked interrupt

1: Unmasked interrupt

Bit 8 OPEM: OUT packet error mask

0: Masked interrupt

1: Unmasked interrupt

Bits 7:3 Reserved, must be kept at reset value.

Bit 2 AHBERRM: AHB error mask

0: Masked interrupt

1: Unmasked interrupt

Bit 1 EPDM: Endpoint disabled interrupt mask

0: Masked interrupt

1: Unmasked interrupt

Bit 0 XFRCM: Transfer completed interrupt mask

0: Masked interrupt

1: Unmasked interrupt

313029282726252423222120191817161514131211109876543210

EPENA

EPDIS

SODDFRM

SD0PID/SEVNFRM

SNAK

CNAK

TXFNUM

Stall

Reserved

EPTYP

NAKSTS

EONUM/DPID

USBAEP

Reserved

MPSIZ

rsrswwwwrwrwrwrw

rw/

rs

rw rw r r rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...