Chrom-Art Accelerator™ controller (DMA2D) RM0090

368/1749 RM0090 Rev 18

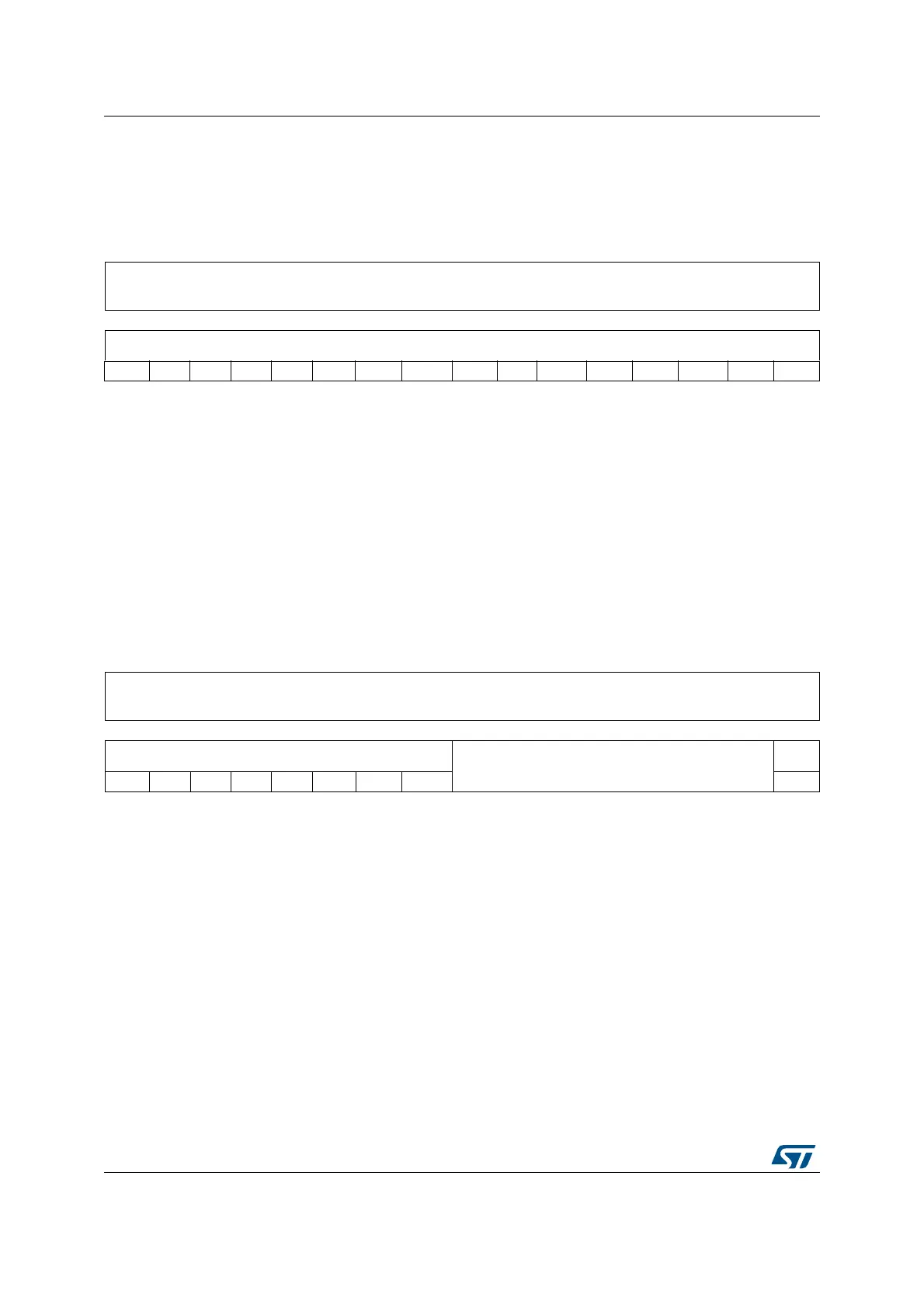

11.5.19 DMA2D line watermark register (DMA2D_LWR)

Address offset: 0x0048

Reset value: 0x0000 0000

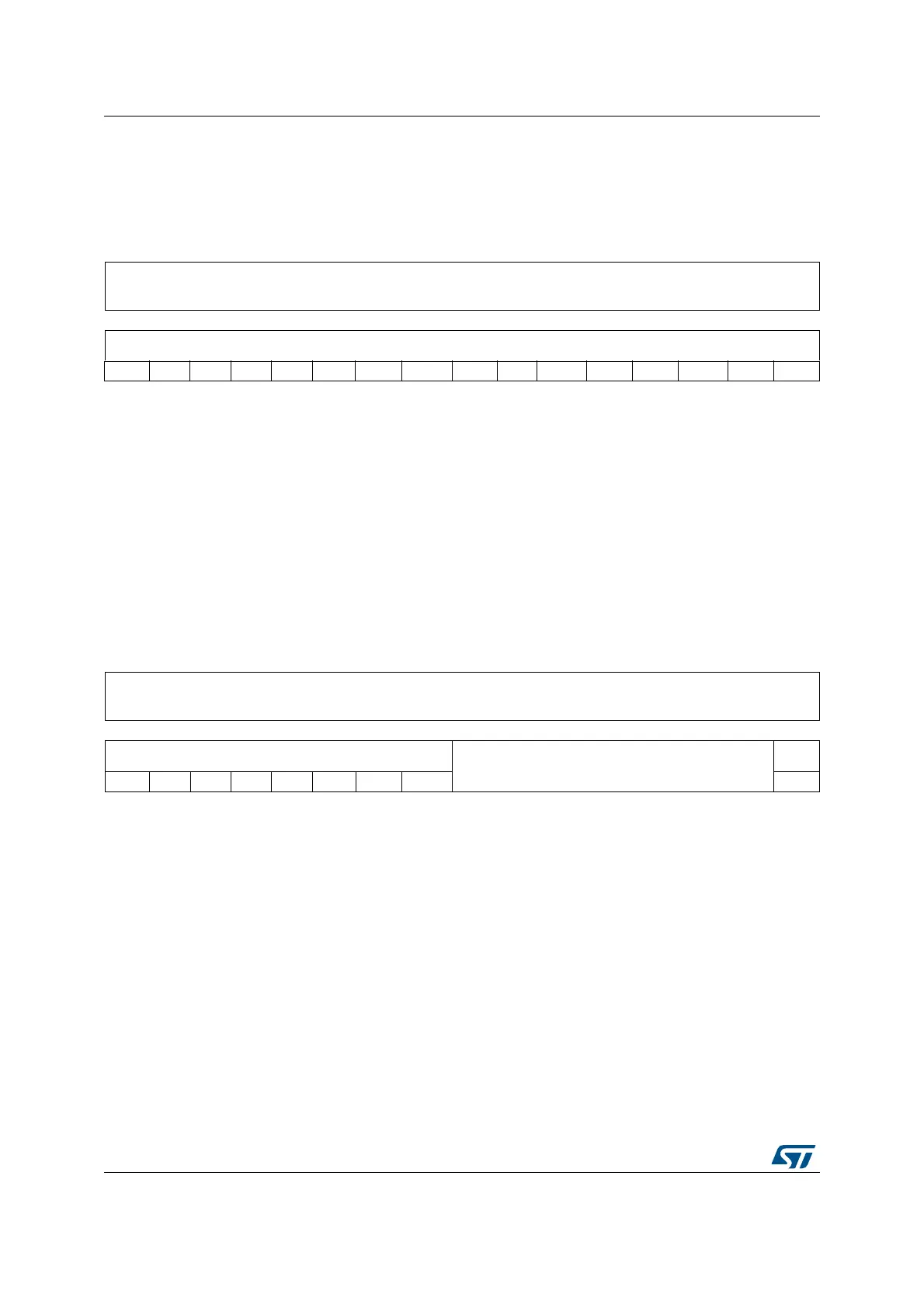

11.5.20 DMA2D AHB master timer configuration register (DMA2D_AMTCR)

Address offset: 0x004C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

LW[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value

Bits 15:0 LW[15:0]: Line watermark

These bits allow to configure the line watermark for interrupt generation.

An interrupt is raised when the last pixel of the watermarked line has been transferred.

These bits can only be written when data transfers are disabled. Once the transfer has

started, they are read-only.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DT[7:0]

Reserved

EN

rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved

Bits 15:8 DT[7: 0]: Dead Time

Dead time value in the AHB clock cycle inserted between two consecutive accesses on

the AHB master port. These bits represent the minimum guaranteed number of cycles

between two consecutive AHB accesses.

Bits 7:1 Reserved

Bit 0 EN: Enable

Enables the dead time functionality.

Loading...

Loading...