RM0090 Rev 18 511/1749

RM0090 LCD-TFT controller (LTDC)

514

16.7.25 LTDC Layerx CLUT Write Register (LTDC_LxCLUTWR)

(where x=1..2)

This register defines the CLUT address and the RGB value.

Address offset: 0xC4 + 0x80 x (Layerx -1), Layerx = 1 or 2

Reset value: 0x0000 0000

Note: The CLUT write register should only be configured during blanking period or if the layer is

disabled. The CLUT can be enabled or disabled in the LTDC_LxCR register.

The CLUT is only meaningful for L8, AL44 and AL88 pixel format.

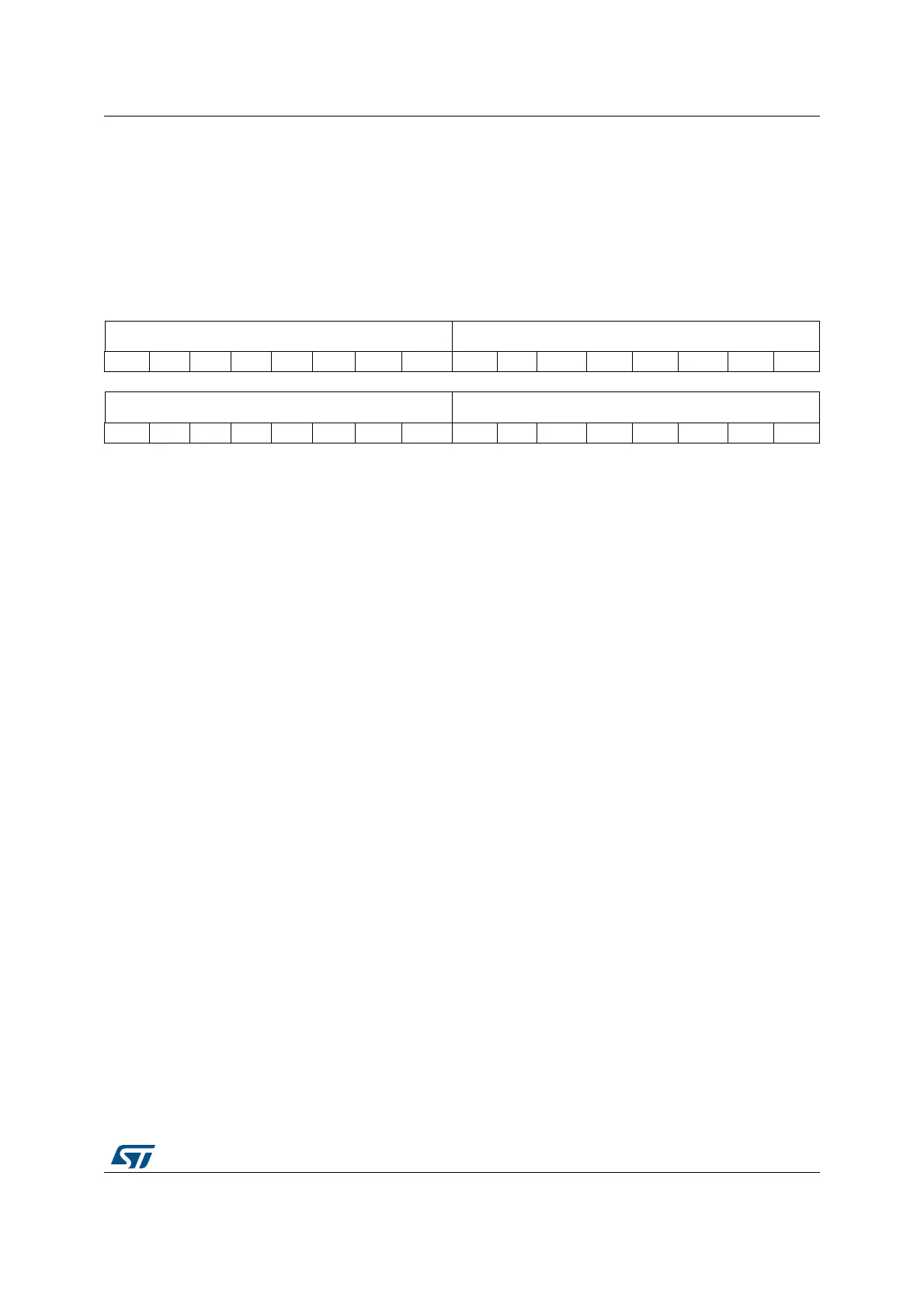

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

CLUTADD[7:0] RED[7:0]

wwwwww w w ww w w w w w w

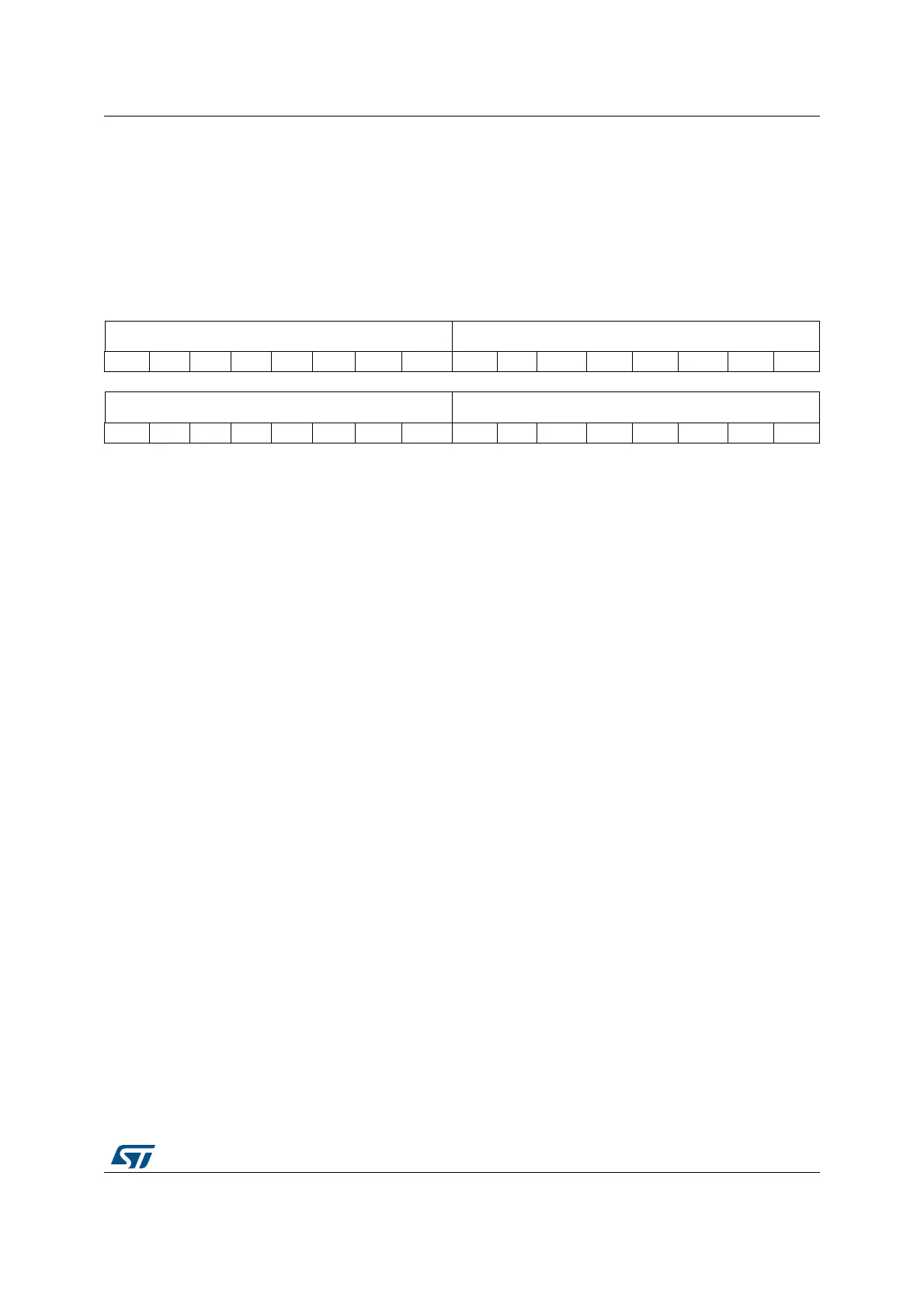

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

GREEN[7:0] BLUE[7:0]

wwwwww w w ww w w w w w w

Bits 31:24 CLUTADD[7:0]: CLUT Address

These bits configure the CLUT address (color position within the CLUT) of each RGB

value

Bits 23:16 RED[7:0]: Red value

These bits configure the red value

Bits 15:8 GREEN[7:0]: Green value

These bits configure the green value

Bits 7:0 BLUE[7:0]: Blue value

These bits configure the blue value

Loading...

Loading...