Serial audio interface (SAI) RM0090

958/1749 RM0090 Rev 18

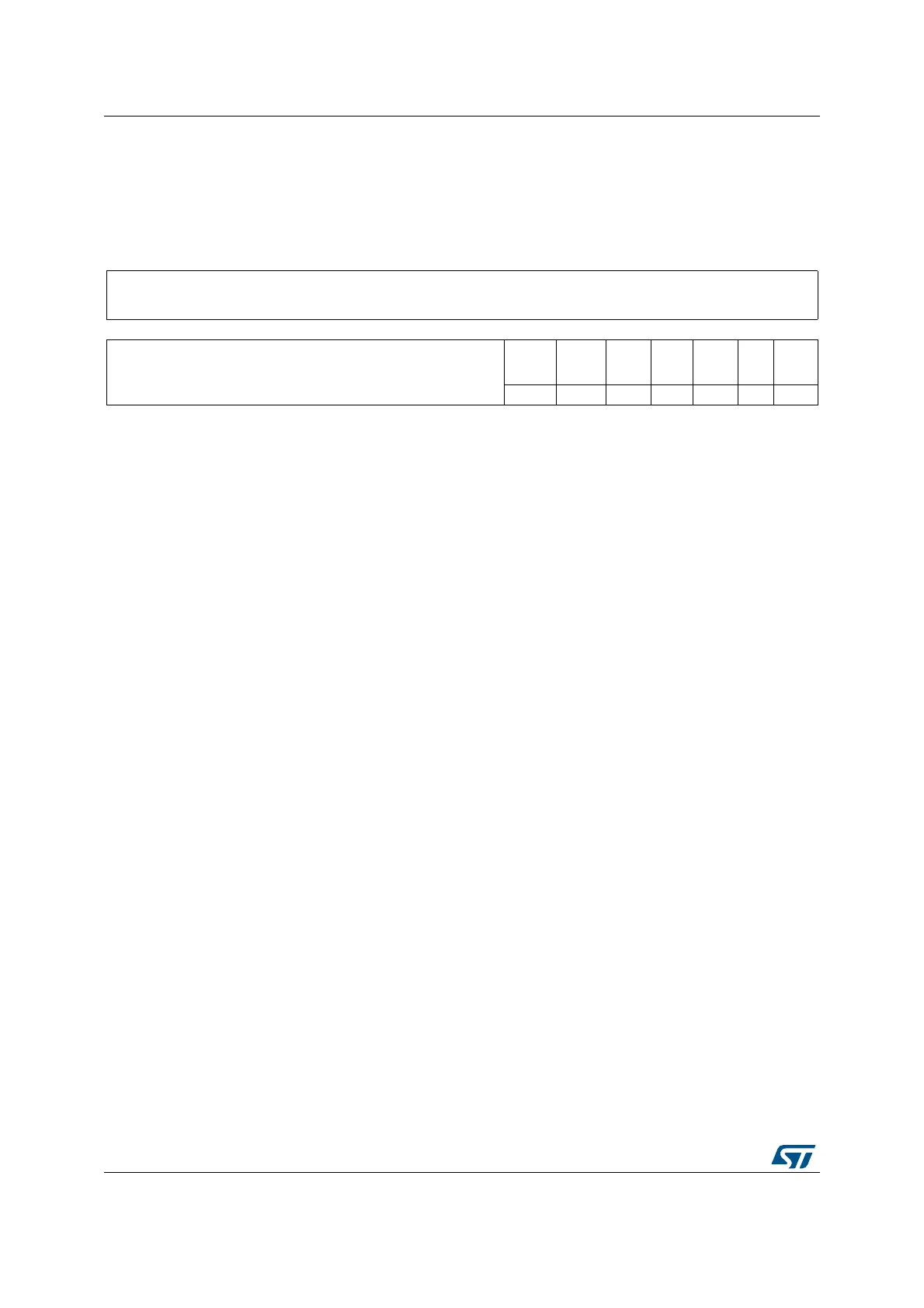

29.17.5 SAI xInterrupt mask register (SAI_xIM) where x is A or B

Address offset: blockA: 0x014

Address offset: block B: 0x034

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

LFSDETI

E

AFSDET

IE

CNRDY

IE

FREQI

E

WCKC

FGIE

MUT

EDET

IE

OVRU

DRIE

rw rw rw rw rw rw rw

Bits 31:7 Reserved, always read as 0.

Bit 6 LFSDETIE: Late frame synchronization detection interrupt enable. This bit is set and cleared by

software.

0: Interrupt is disabled

1: Interrupt is enabled

When this bit is set, an interrupt will be generated if the LFSDET bit is set in the SAI_ASR register.

This bit has no meaning in AC’97 mode. It has no meaning also if the audio block is master.

Bit 5 AFSDETIE: Anticipated frame synchronization detection interrupt enable. This bit is set and cleared by

software.

0: Interrupt is disabled

1: Interrupt is enabled

When this bit is set, an interrupt will be generated if the AFSDET bit in the SAI_ASR register is set.

This bit has no meaning in AC’97 mode. It has no meaning also if the audio block is master.

Bit 4 CNRDYIE: Codec not ready interrupt enable (ac’97). This bit is set and cleared by software.

0: Interrupt is disabled

1: Interrupt is enabled

When the interrupt is enabled, the audio block will detect in the slot 0 (tag0) of the AC’97 frame if the

codec connected on this line is ready or not. If not, the flag CNRDY in the SAI_ASR register will be

set and an interruption will be generated.

This bit has a meaning only if the AC97 mode is selected (bit PRTCFG[1:0]) and the audio block is a

receiver.

Bit 3 FREQIE: FIFO request interrupt enable. This bit is set and cleared by software.

0: Interrupt is disabled

1: Interrupt is enabled

When this bit is set, an interrupt will be generated if the FREQ bit in the SAI_ASR register is set.

In receiver mode, the bit MODE must be configured before setting bit FREQIE to avoid a parasitic

interruption since the audio block is a transmitter (default setting).

Loading...

Loading...