Controller area network (bxCAN) RM0008

658/1096 Doc ID 13902 Rev 12

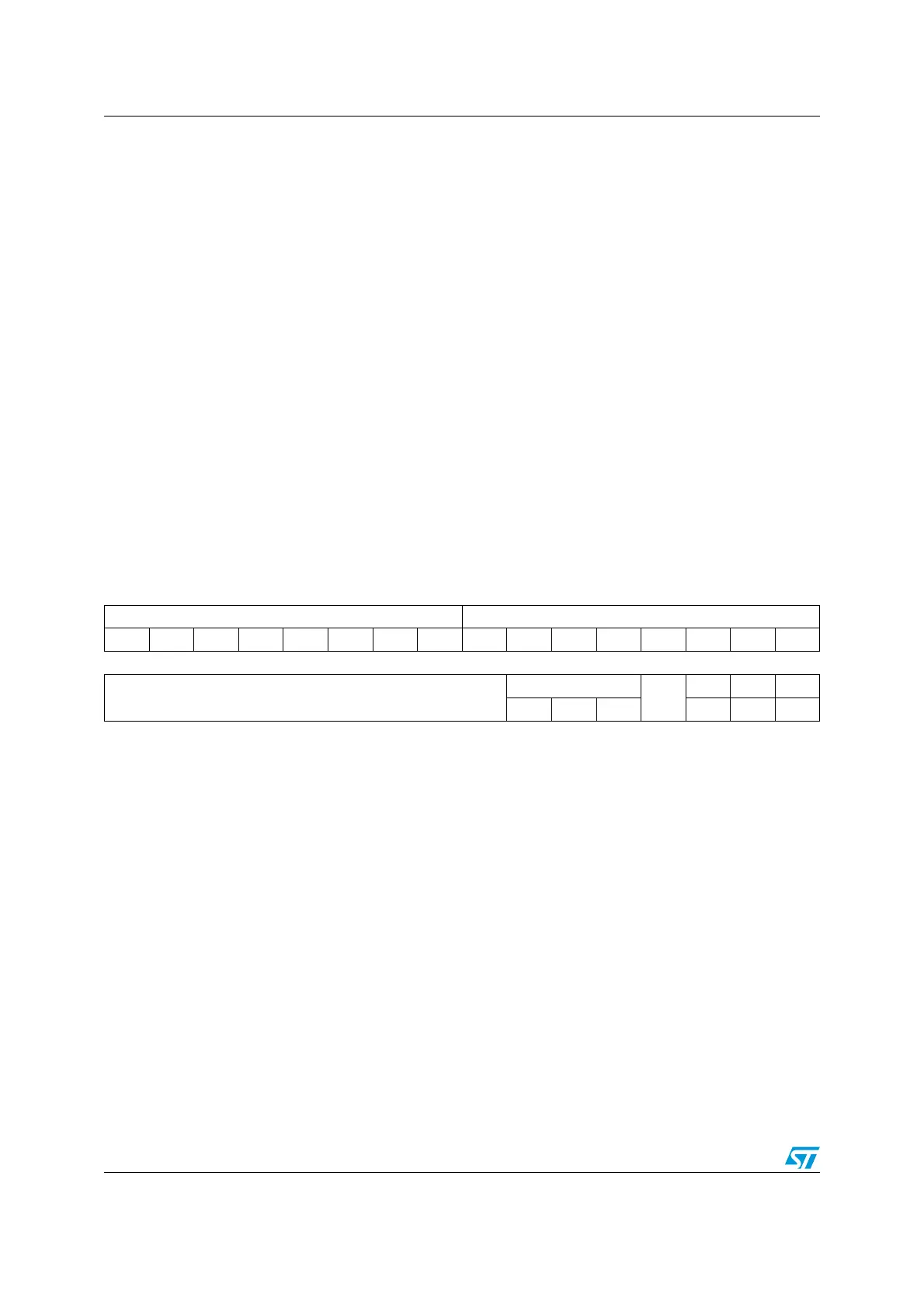

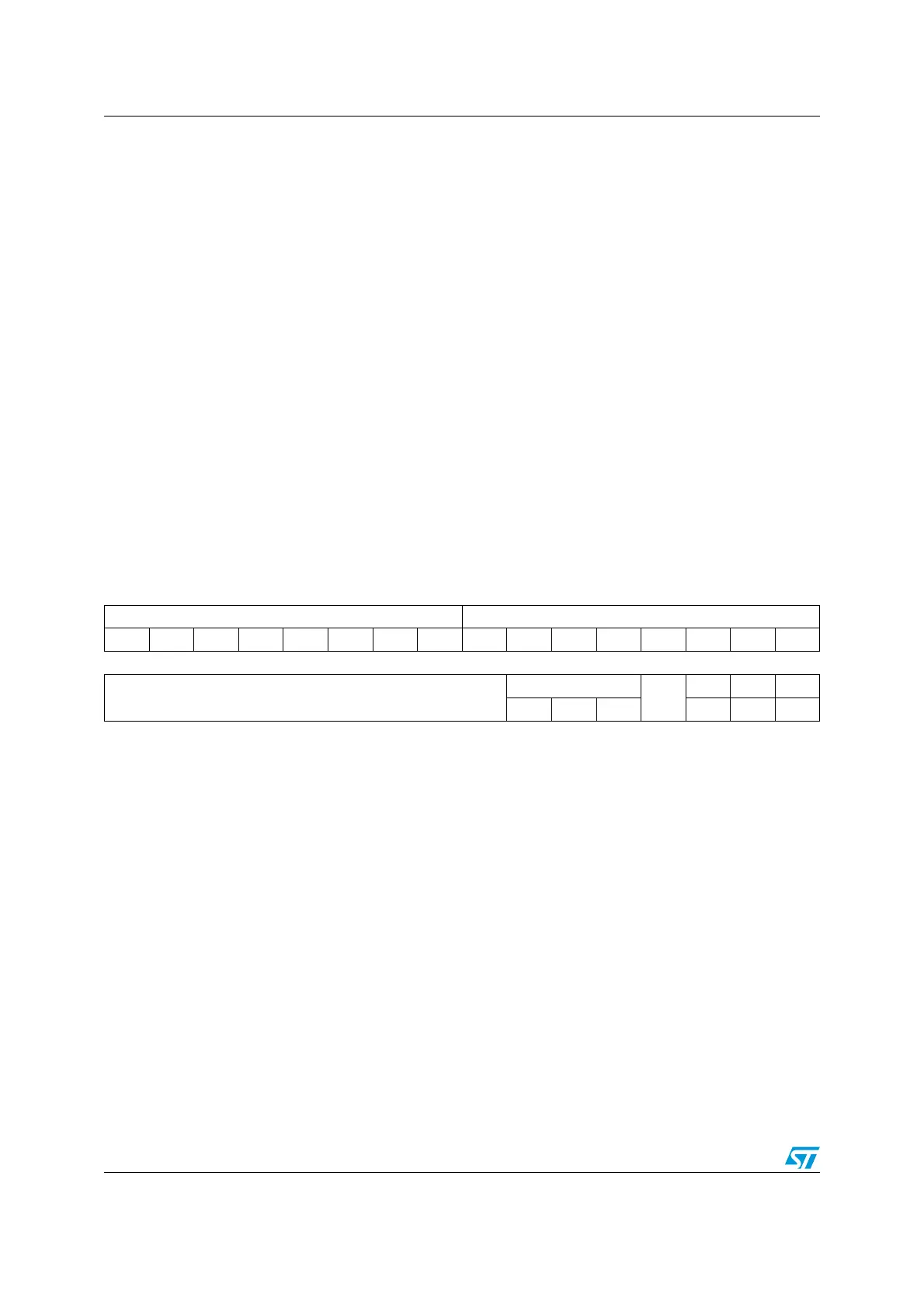

CAN error status register (CAN_ESR)

Address offset: 0x18

Reset value: 0x00

Bit 4 FMPIE1: FIFO message pending interrupt enable

0: No interrupt generated when state of FMP[1:0] bits are not 00b.

1: Interrupt generated when state of FMP[1:0] bits are not 00b.

Bit 3 FOVIE0

: FIFO overrun interrupt enable

0: No interrupt when FOVR bit is set.

1: Interrupt generated when FOVR bit is set.

Bit 2 FFIE0

: FIFO full interrupt enable

0: No interrupt when FULL bit is set.

1: Interrupt generated when FULL bit is set.

Bit 1 FMPIE0: FIFO message pending interrupt enable

0: No interrupt generated when state of FMP[1:0] bits are not 00b.

1: Interrupt generated when state of FMP[1:0] bits are not 00b.

Bit 0 TMEIE

: Transmit mailbox empty interrupt enable

0: No interrupt when RQCPx bit is set.

1: Interrupt generated when RQCPx bit is set.

Note: Refer to Section 24.8: bxCAN interrupts.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

REC[7:0] TEC[7:0]

rrrrrrrrrrrrrrrr

1514131211109876543210

Reserved

LEC[2:0]

Res.

BOFF EPVF EWGF

rw rw rw r r r

Bits 31:24 REC[7:0]: Receive error counter

The implementing part of the fault confinement mechanism of the CAN protocol. In case of

an error during reception, this counter is incremented by 1 or by 8 depending on the error

condition as defined by the CAN standard. After every successful reception the counter is

decremented by 1 or reset to 120 if its value was higher than 128. When the counter value

exceeds 127, the CAN controller enters the error passive state.

Bits 23:16 TEC[7:0]

: Least significant byte of the 9-bit transmit error counter

The implementing part of the fault confinement mechanism of the CAN protocol.

Bits 15:7 Reserved, forced by hardware to 0.

Loading...

Loading...