RM0090 Rev 18 499/1749

RM0090 LCD-TFT controller (LTDC)

514

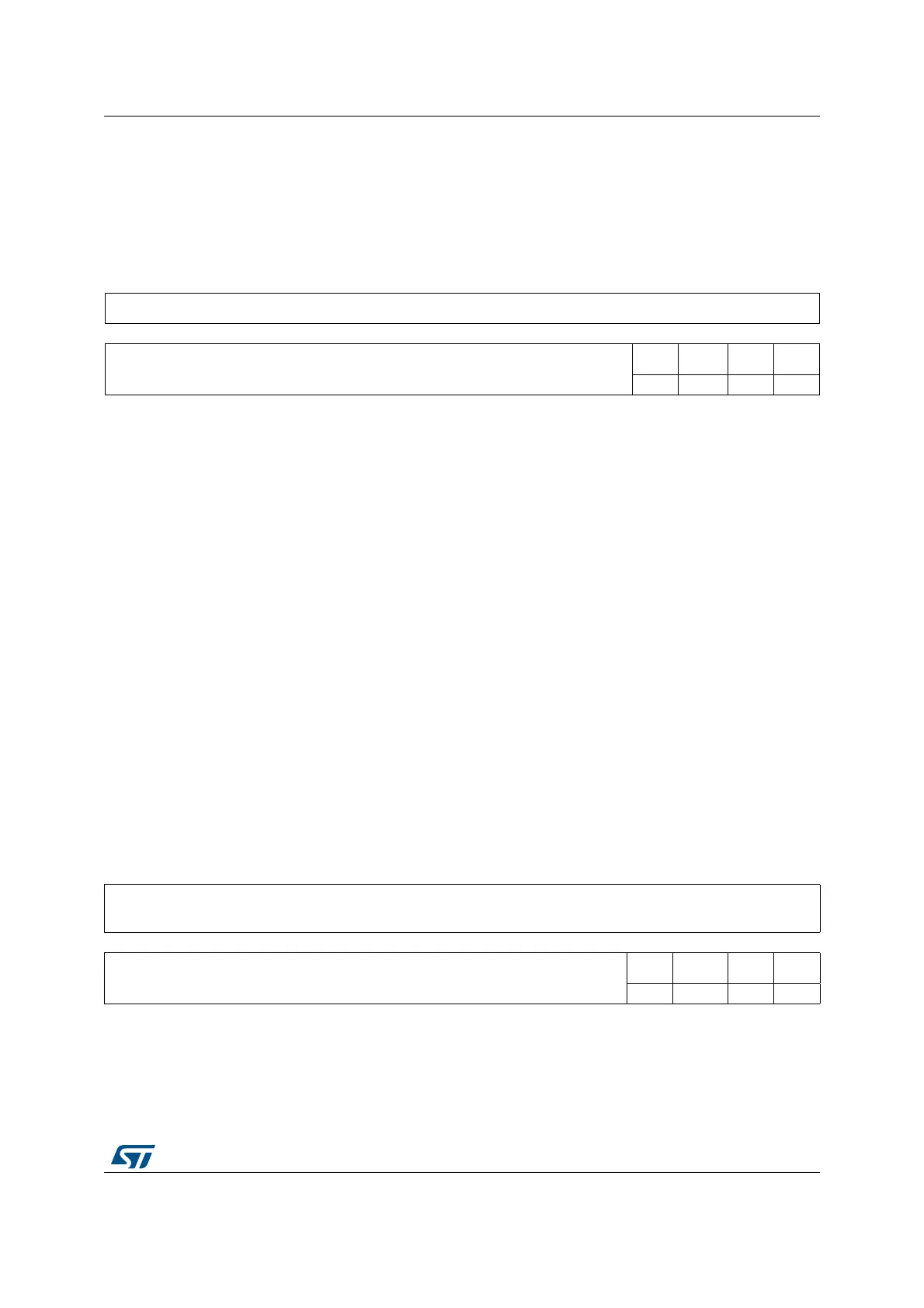

16.7.9 LTDC Interrupt Status Register (LTDC_ISR)

This register returns the interrupt status flag

Address offset: 0x38

Reset value: 0x0000 0000

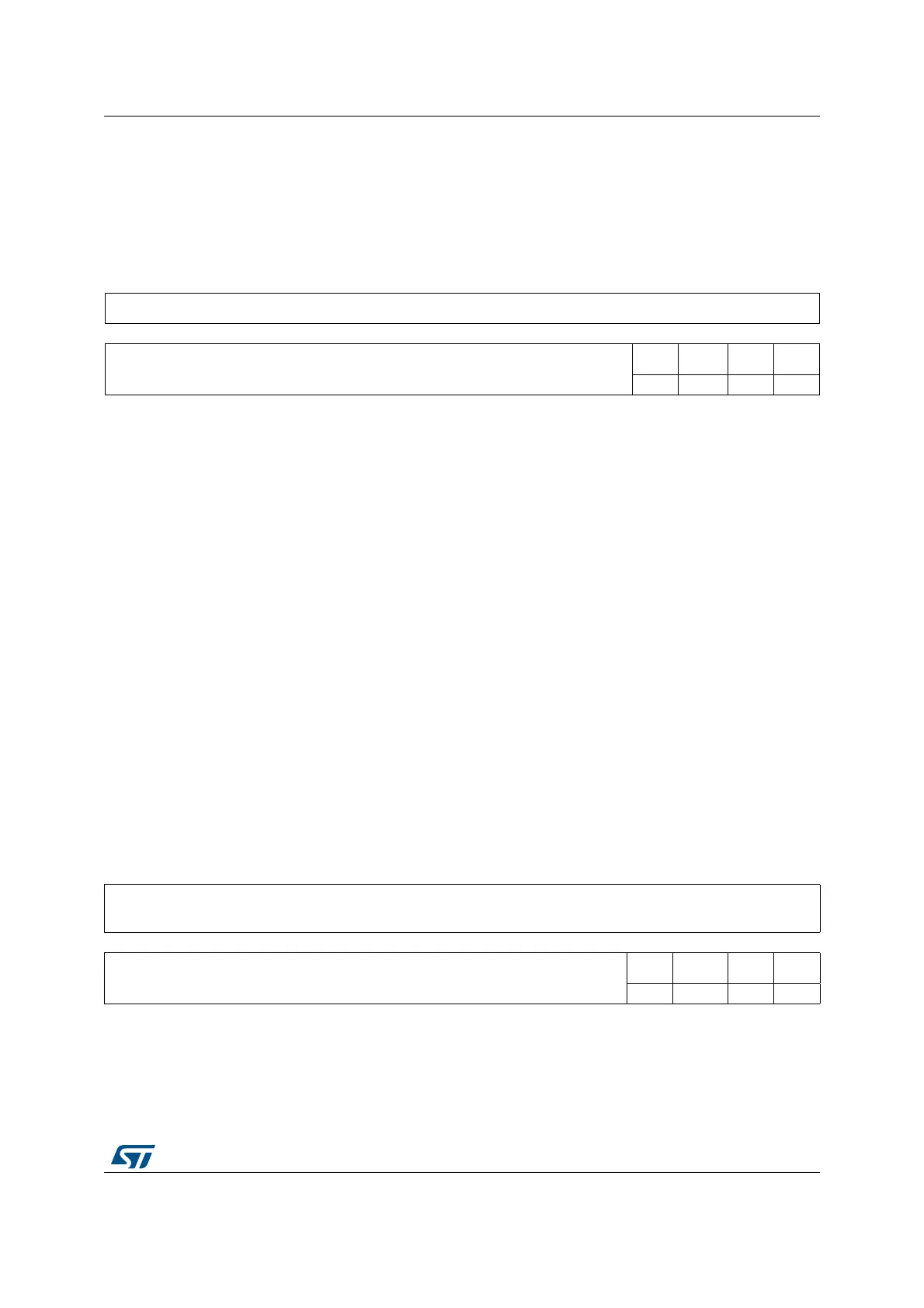

16.7.10 LTDC Interrupt Clear Register (LTDC_ICR)

Address offset: 0x3C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

RRIF TERRIF FUIF LIF

rrrr

Bits 31:24 Reserved, must be kept at reset value

Bit 3 RRIF: Register Reload Interrupt Flag

0: No Register Reload interrupt generated

1: Register Reload interrupt generated when a vertical blanking reload occurs (and the

first line after the active area is reached)

Bit 2 TERRIF: Transfer Error interrupt flag

0: No Transfer Error interrupt generated

1: Transfer Error interrupt generated when a Bus error occurs

Bit 1 FUIF: FIFO Underrun Interrupt flag

0: NO FIFO Underrun interrupt generated.

1: A FIFO underrun interrupt is generated, if one of the layer FIFOs is empty and pixel

data is read from the FIFO

Bit 0 LIF: Line Interrupt flag

0: No Line interrupt generated

1: A Line interrupt is generated, when a programmed line is reached

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

CRRIF CTERRIF CFUIF CLIF

wwww

Loading...

Loading...