EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 106

Universal Serial Bus (USB)

break;

default:

break;

}

}

/* If there has been an error, stall EP0 to fail the transaction. */

if ((isHandled != CyTrue) || (status != CY_U3P_SUCCESS))

{

/* This is an unhandled setup command. Stall the EP. */

CyU3PUsbStall (0, CyTrue, CyFalse);

}

}

6.9.8 USB Embedded Host

The FX3 embedded host works in the same way as a standard USB 2.0 host. The FX3 firmware prepares a scheduler table

with USB transfer entries that are similar to the Transfer Descriptor (TD) tables maintained by PC hosts. The actual transfer

scheduling is done by hardware to eliminate the overheads caused by the firmware managed scheduling.

6.9.8.1 Clocking

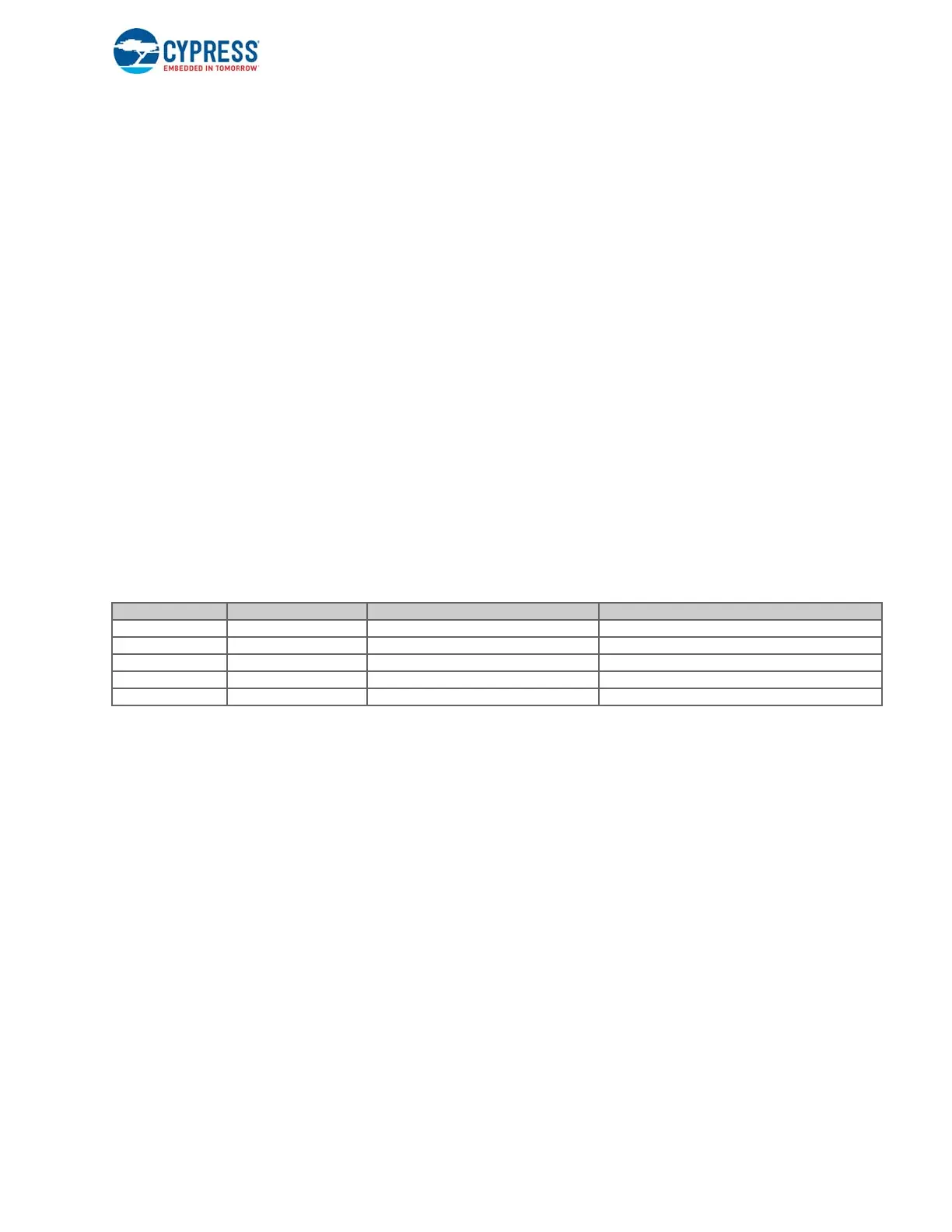

There are five independent clock domains in the UIB block supporting the USB 2.0 host functions, as listed in Ta b l e 6- 4 .

Table 6-4. USB 2.0 Embedded Host Clocks

In addition, the endpoint memory uses a clock, uib_epm_clk_i, that is 100 MHz when the USB 2.0 host is active. The

uib_epm_clk_i configuration source is from GCTL_UIB_CORE_CLK.EPMCLK_SRC and enabled by

GCTL_UIB_CORE_CLK.CLK_EN.

6.9.9 Interrupt Requests

The USB 2.0 host interrupts are part of the main USB core interrupt.

USB 2.0 OHCI interrupts are located in UIB_OHCI_INTERRUPT_STATUS. UIB_INTR.HOST_INT is the logical OR of the

interrupt sources in UIB_OHCI_INTERRUPT_STATUS.

USB 2.0 EHCI interrupts are located in UIB_EHCI_USBINTR. UIB_INTR.HOST_INT is the logical OR of the interrupt sources

in UIB_EHCI_USBINTR.

USB 2.0 host endpoint interrupts are located in UIB_HOST_EP_INTR. UIB_INTR.HOST_EP_INT is the logical OR of the

interrupt sources in UIB_HOST_EP_INTR.

USB charger detect interrupts are located in UIB_CHGDET_INTR. UIB_INTR.CHGDET_INT is the logical OR of the interrupt

sources in UIB_CHGDET_INTR.

Domain Typ Freq Configuration Source Description

dma_bus_clk_i 100 MHz GCTL_CPU_CLK_CFG.DMA_DIV DMA access clock

mmio_bus_clk_i 100 MHz GCTL_CPU_CLK_CFG.MMIO_DIV MMIO register access clock

uib_sieclock_i 30 MHz Driven from USB 2.0 OTG PHY USB 2.0 serial interface engine clock

standby_clk_i 32 kHz Always-on Always-on clock for low-power modes

uib_ref_clk_i 19.2/26/38.4/52 MHz External input clock USB2.0 PHY reference clock

Loading...

Loading...