EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 148

General Programmable Interface II (GPIF II)

A set of rules needs to be satisfied by all the mirror state machines. GPIF II Designer tries to identify a set of global triggers

that reduce the state machine to one that satisfies the following rules.

■ The transitions can be split into groups of two each, such that each group applies to a specific combination of trigger val-

ues.

■ The transitions in each group have the same transition equations after the global trigger terms have been removed.

■ The target states that share the same transition equation do not use conflicting actions. See Ta bl e 7- 2 for details on

incompatible actions.

The tool first attempts to find a solution with one global trigger, then with two, and finally three global triggers. If the tool is

unable to find a state machine reduction that satisfies the previous conditions with any of these levels, it will issue an error

message saying that the state machine input cannot be synthesized.

In many cases, such state machine mapping errors are a consequence of an incompletely specified input. See 7.7.4

Guidelines for Transition Equation Entry on page 149 for state machine definition guidelines to aid the tool in finding a

solution.

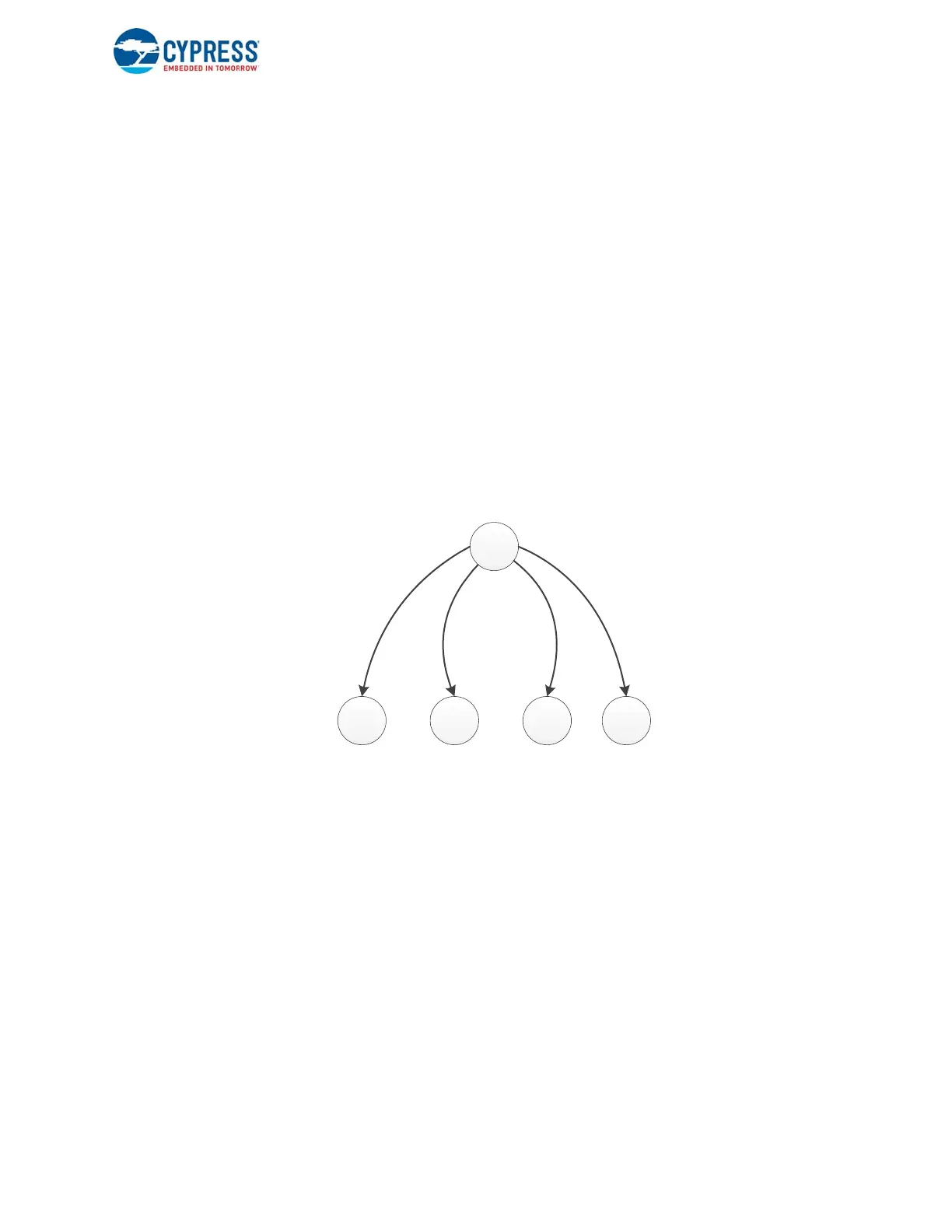

7.7.3 Mirror State Example

Figure 7-32 shows a part of the synchronous Slave FIFO protocol implementation that is included with GPIF II Designer as a

Cypress supplied interface project.

Figure 7-32. Slave FIFO Interface Example State Machine Requiring Mirror States

The IDLE state is where the state machine waits for control signals to start performing a data transfer. Depending on the input

signals, it may transition to one of four states:

The RD state, where a read operation is handled. Transition to the RD state is triggered by the RD input signal asserting while

the WR and the END input signals are deasserted. The IN_ADDR and DR_DATA actions are performed in the RD state.

The WR state, where a general write operation (not end of packet) is handled. Transition to the WR state is triggered by the

WR input asserting while the RD and END signals are deasserted. The IN_DATA action is associated performed with this

state.

The SLP state, where a single word write operation is handled (data along with end-of-packet signaling). Transition to the SLP

state is triggered by the WR and END inputs asserting while RD is deasserted. The IN_DATA and COMMIT actions are

associated with this state.

The ZLP state, where a zero-length write operation is handled (no data, only end-of-packet signaling). This transition is

triggered by END asserting while RD and WR are both deasserted. The COMMIT action is associated with this state.

IDLE

RD WR SLP ZLP

R

D

&

!

W

R

&

!

E

N

D

!

R

D

&

W

R

&

!

E

N

D

!

R

D

&

W

R

&

E

N

D

!

R

D

&

!

W

R

&

E

N

D

IN_ADDR

DR_DATA

IN_DATA

IN_DATA

COMMIT

COMMIT

Loading...

Loading...